# **Understanding the Apple IIe**

# by Jim Sather

Foreword by Steve Wozniak

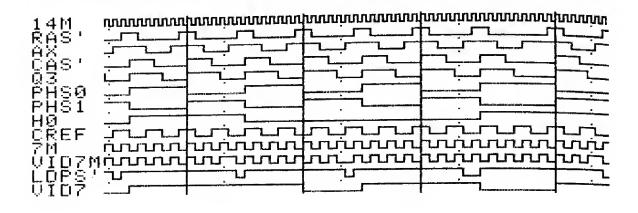

# Understanding the Apple IIe

by James Fielding Sather

BRADY COMMUNICATIONS, CO., INC. A Prentice-Hall Publishing Company BOWIE, MARYLAND 20715 Quality Software 21601 Marilla Street Chatsworth, CA 91311

| Apple Books from Quality Software                                                                                                                                                                                                                                                                                |         |

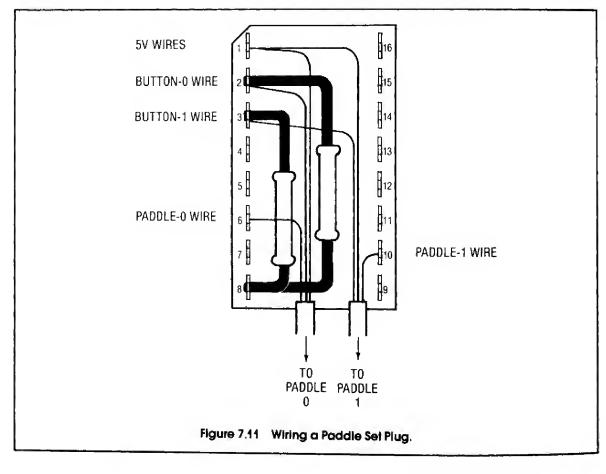

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Understanding the Apple II by Jim Sather<br>The companion to Understanding the Apple IIe, this book is the<br>definitive source of information about the Apple II and Apple II Plus.                                                                                                                             | \$22.95 |

| Beneath Apple DOS by Don Worth and Pieter Lechner<br>The popular best seller that tells all about DOS 3.3.                                                                                                                                                                                                       | \$19.95 |

| Beneath Apple ProDOS by Don Worth and Pieter Lechner<br>A critical, non-Apple explanation of how ProDOS works. Describes<br>how to use ProDOS with custom programming applications.                                                                                                                              | \$19.95 |

| Apple Utility Software from Quality Software                                                                                                                                                                                                                                                                     |         |

| Bag of Tricks (includes diskette) by Don Worth and Pieter Lechner<br>The best set of DOS-based disk utilities available. Four programs<br>in one. Edit disk sectors, reformat single tracks, repair catalogs.                                                                                                    | \$39.95 |

|                                                                                                                                                                                                                                                                                                                  | 004.05  |

| <ul> <li>Universal File Conversion (includes diskette) by Gary Charpentier</li> <li>Move data between DOS 3.3, CP/M, Apple Pascal, SOS, and ProDOS.</li> <li>Format disks for any OS. Create CP/M files without a Softcard.</li> <li>48-page manual explains how each OS stores different file types.</li> </ul> | \$34.95 |

1. Deales from Quality Software

Ask for these fine products at your local computer store or bookstore. Or call Quality Software direct, (818) 709-1721.

Production Editor: Kathryn M. Schmidt Editorial Assistant: Tom Weinstein Original Schematics and Diagrams: James Fielding Sather Art Director and Cover Design: Vic Grenrock Cover Art: George Garcia Schematic Art and Compositor: Ron Widman Photography: Gainsforth Studios Printed By: Griffin Printing

<sup>©</sup> 1985 Quality Software. All rights reserved. No part of this book may be reprinted, or reproduced, or utilized in any form or by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying and recording, or in any information storage and retrieval system, without permission in writing from the Publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

ISBN 0-8359-8019-7

87 86 85 54321

Printed in the United States of America

## foreword

I will never forget the first conversation I had with Jim Sather. He was then in the process of writing his first book, Understanding the Apple II. Jim and I discussed the details, anomalies, oversights, and paradoxes of the Apple II hardware as we drove the LA freeways. Designers like myself find it very rewarding to encounter others who understand and appreciate what we feel are the tricks and magic of our circuits. I was able to add to the magic by explaining the unusual framework in which the computer was designed. From my conversations with him, and from his writing, it is obvious that Jim has a contagious enthusiasm about Apple computers, and this enthusiasm is sure to spread to readers of his books. In Understanding the Apple II, Jim provided the definitive treatment of Apple II hardware. He has now followed that effort with the equally definitive Understanding the Apple IIe.

Patterned after the earlier book, Understanding the Apple IIe leaves no stone unturned in the search into the inner workings of the Apple IIe computer. All facets of the Apple are revealed, from basic microprocessor operation to the inner secrets of the Apple IIe custom ICs. Disk controller operation—my favorite subject—is explained in great detail. Numerous programming examples illustrate the application of hardware knowledge.

Anyone who is at all concerned about the workings of the Apple IIe will benefit from this book, as will students and programmers who have a need for reliable hardware reference material. It is an inclusive source for a great variety of Apple IIe information. The Apple IIe holds a special niche in the history of microcomputers. Documentation of this quality is worthy of the computer it describes.

## preface

It has been close to a decade since an unknown kid, having some fun in his own creative way, built the first Apple computer. What a difference a decade makes, Our boy is well known now, and he and his pals have built millions of Apples with which millions of people have had a tremendous amount of fun in their own creative ways.

The creative ways of different people lead them in different directions, and not all Apple owners use their computer for the same purposes. Yet diverse as they are, people who use their Apple have a common need for knowledge and understanding of the workings of the computer. Most of them will teach themselves almost everything they learn about the Apple, so they also have a need for tutorial literature and meaningful reference material to guide them down their chosen paths.

The purpose of Understanding the Apple He is to provide tutorial descriptions and reference material concerning the most basic of Apple He related knowledge. It contains explanations of how the hardware works and how programmers make the hardware work. Emphasis is placed on assisting the reader in attaining operational knowledge of the Apple He. Operational knowledge consists of knowing what the Apple He can do, knowing how to make it do it, and knowing what a controlling program is making the Apple He do. By way of assisting the reader in achieving his goals, the goals of this book are:

- 1. To provide clear descriptions of microcomputer fundamentals and of the operational features of the Apple IIe.

- 2. To provide examples that show how knowledge of the operational features of the Apple IIe can be applied.

- 3. To provide meaningful reference material concerning Apple IIe hardware and operational features.

- 4. To serve as a textbook for Apple-based high school or university courses teaching computer fundamentals.

- 5. To fill information gaps in Apple IIe literature by describing previously undocumented operational features.

Those who will benefit from reading Understanding the Apple IIe are inquiring people who want to spend some time learning about this machine. Generally speaking, this refers to those persons who program the Apple IIe in any language. It is recognized that different people will carry their investigation to different depths. For those who do not have the time or desire to reach the greater depths, the overview, bus structure, and I/O chapters (Chapters 1, 2, and 7), as well as the application notes at the end of every chapter, are recommended as providing a good foundation for understanding the Apple IIe. As a textbook for students or a learning guide to hard core enthusiasts, cover to cover reading is recommended.

While an inquiring mind is the only qualification required of a reader of this book, certain sections will be difficult for those readers without some background knowledge. In order of descending importance, helpful background knowledge includes understanding of BASIC programming language, hexadecimal and binary number systems, 6502 assembly language, and technical illustrative aids such as timing diagrams, truth tables, and schematic diagrams. It should be noted by all readers that (except for the technical aids) they will eventually have to acquire the listed background knowledge if they are to achieve a real understanding of the Apple IIe computer. It is hoped that the nontechnical aids and language in Understanding the Apple He are sufficiently descriptive, and that a technical background, although helpful, is not necessary. In general, the later chapters contain more detailed and technical information than the earlier chapters, and the earlier sections in each chapter are less technically oriented. Appendices E and F contain some basic information on number systems and circuit symbols for those readers who come to this book with no previous knowledge of these subjects.

Even though Understanding the Apple IIe is not a programming instruction manual, many programming examples that illustrate applications of the principles being discussed are given in the body of the text. Where possible, these examples are written in BASIC so that the clearest attainable level of illustration results. In addition, a number of software application notes are included at the end of various chapters which further demonstrate the application of principles. These programming notes are included because understanding the Apple IIe includes a combination of programming knowledge and hardware knowledge. Unless noted otherwise, all software examples are creations of the author and are hereby placed in the public domain. The author requests that he be given credit as the programmer in all reproductions of these programs.

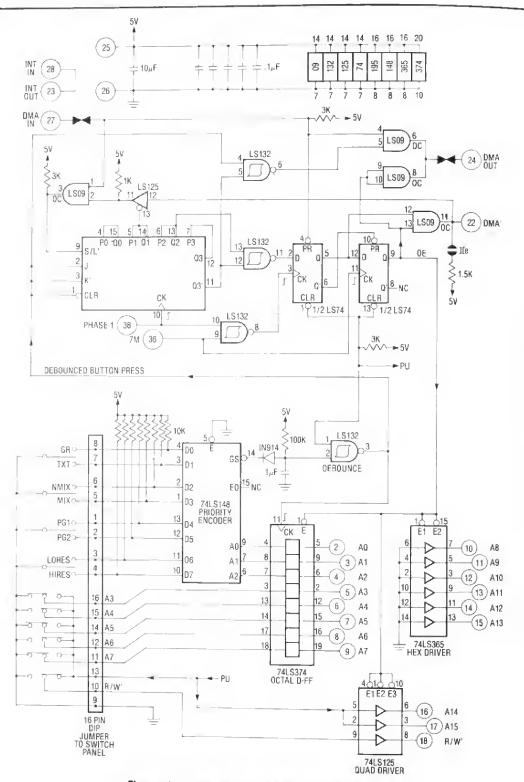

A number of hardware application notes are also included at the ends of chapters. Some of these notes describe hardware projects which demonstrate relevant principles. Other notes are simple descriptions of hardware modifications that enhance operation in some way. Figure 4.7 is an original design of the author. Readers are encouraged to study, build, or integrate it into their own designs. The author requests that he be given credit as the designer in any reproduction or other use of this schematic. The D MAnual Controller is being manufactured by the Southern California Research Group, and is available by mail as noted in Chapter 4.

Several hardware application notes detail modifications to the Apple or Apple peripherals. Please read the NOTE OF CAUTION following the Table of Contents before performing any modifications to your equipment. It is recommended that readers unskilled in electronics workmanship who desire a modification have the work performed at a computer dealership or by a skilled friend. Persons who modify their hardware should be able, or know someone who is willing and able, to repair the modified assembly if it should fail.

Understanding the Apple IIe is the companion of my previously published work, Understanding the Apple II\*. These two books are identical in format and outline, one describing the Apple II computer and the other describing the Apple IIe. Readers of both books will find that, where operational features in the two computers are identical, the text in the two books is identical. Those readers will also find that some application notes which are relevant to both the Apple II and Apple IIe are found in both books. To the extent that operational features and hardware implementation in the Apple IIe is different than that of the Apple II, Understanding the Apple IIe is different from Understanding the Apple II.

\*Quality Software, 1983.

In deference to readers who have experience only with the Apple IIe, descriptions in *Understanding the Apple IIe* assume that the reader is not familiar with the functioning of the older Apple II. However, Apple II features and functions are sometimes described in order to clarify differences between the two computers or to explain why Apple IIe features exist. Some notes on differences between the Apple II and IIe are contained in Appendix I.

There are differences among Apples that are sold in various regions of the world, and it is sometimes difficult to make statements that are accurate for all versions. Generally, descriptions in this book pertain to the Apple IIe as it is sold in the USA with separate sections devoted to descriptions of export versions. Readers in other countries should be aware that some descriptions, in particular those dealing with signal frequency and video generation, may give details that are not accurate in their country. Those readers should rely on the sections of Chapters 3 and 8 that deal directly with international Apples for guidance. Additionally, it should be noted that program listings in Figures 3.11 and 3.12 have to be modified if they are to operate correctly in 50 Hz display scanning Apples such as those found in Europe.

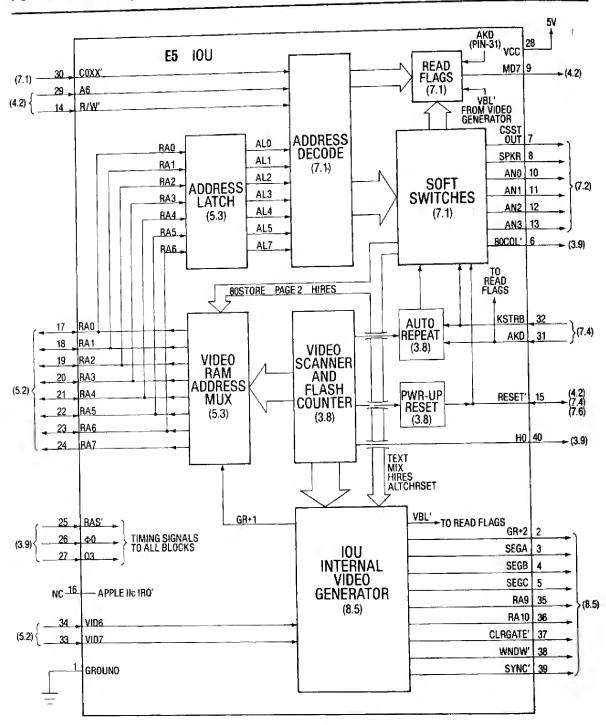

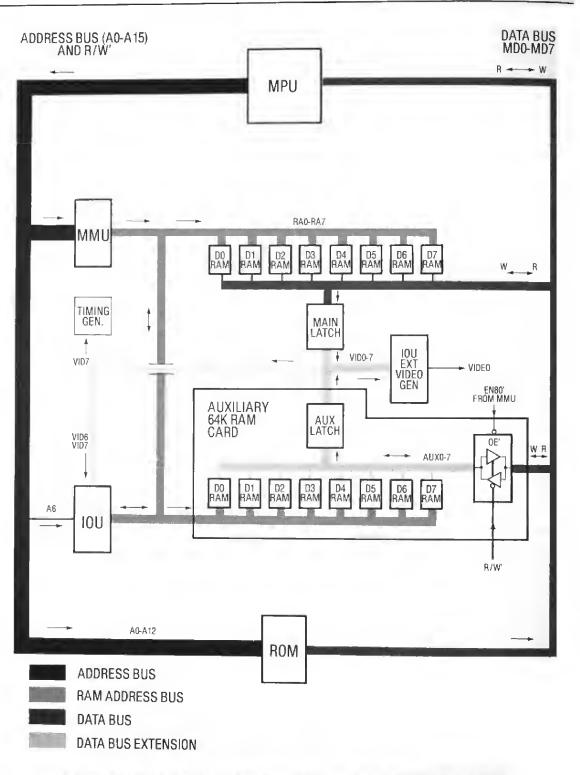

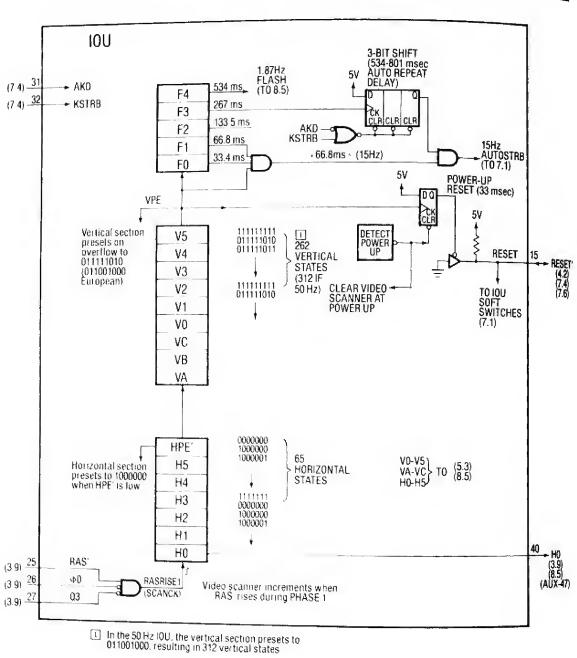

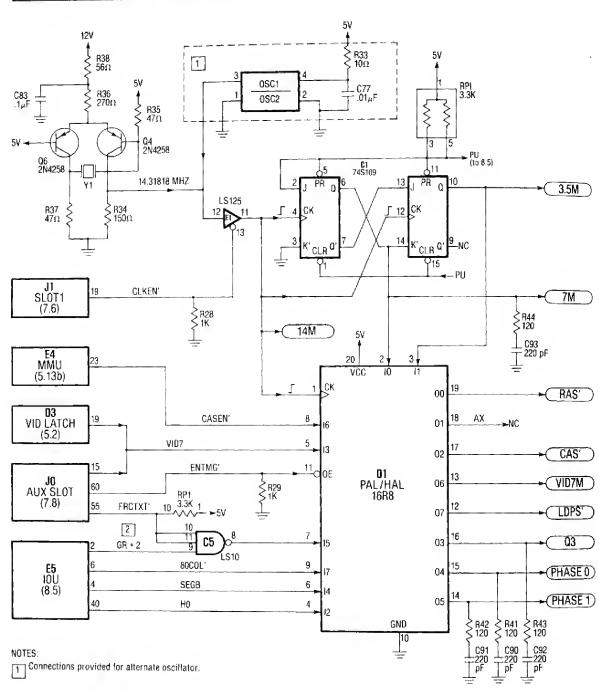

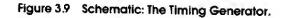

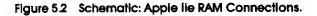

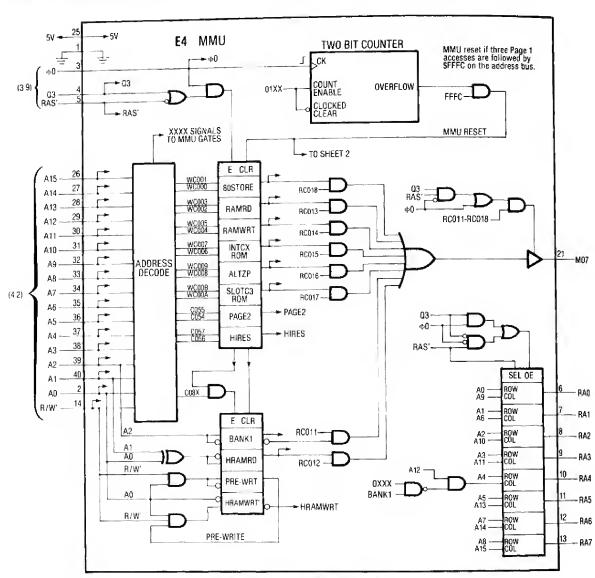

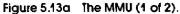

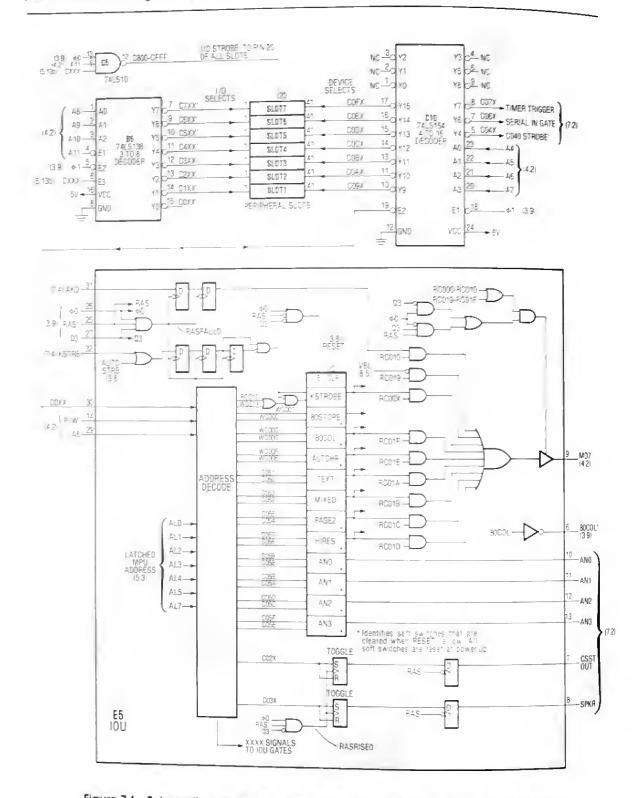

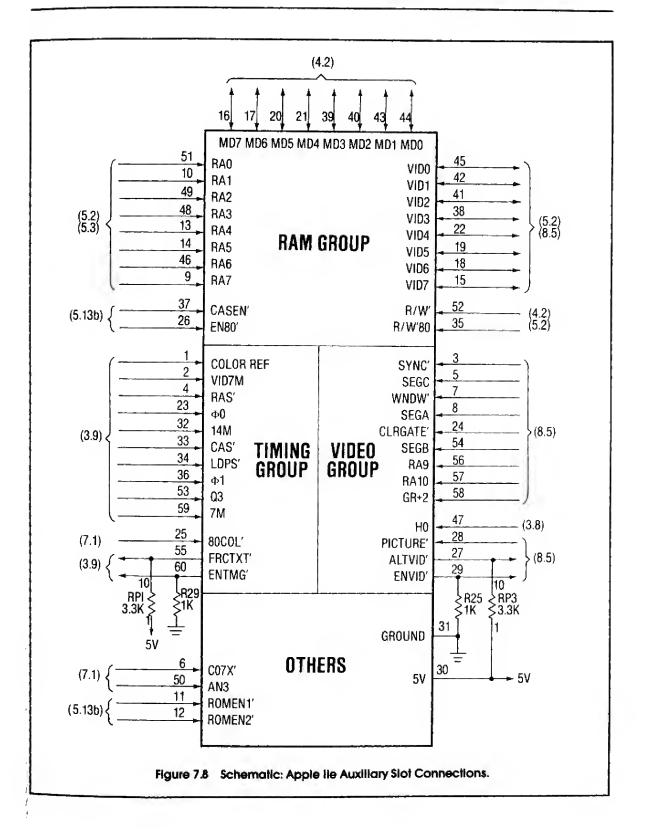

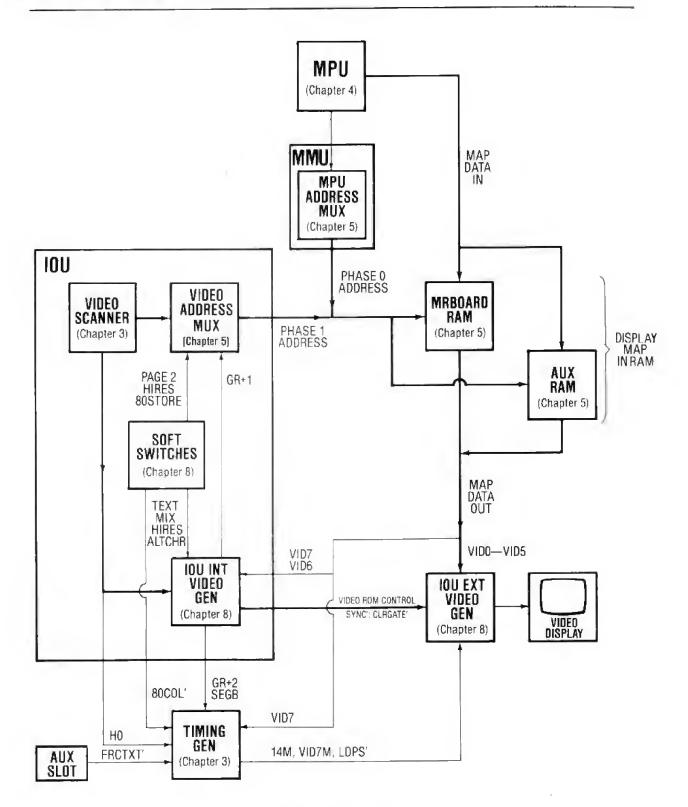

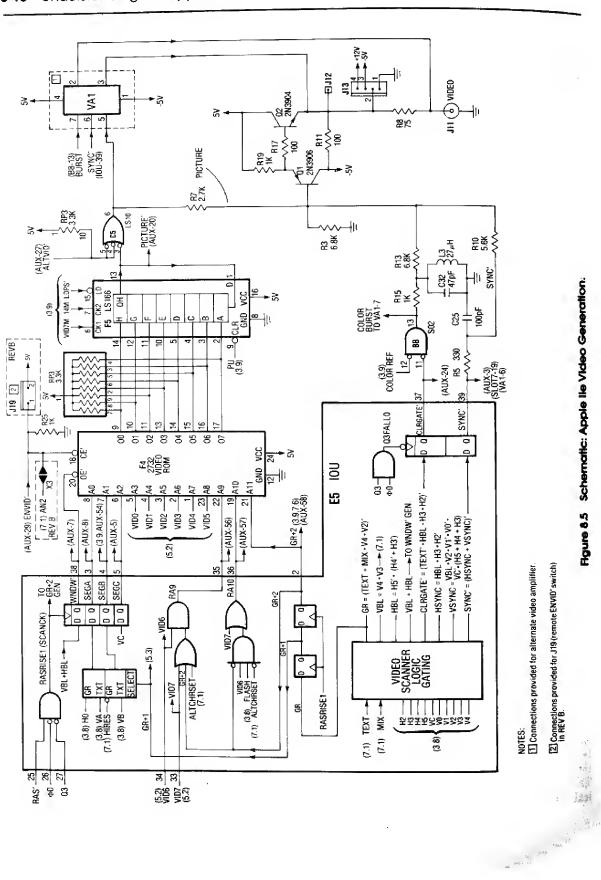

Figures 1.1, 3.8, 3.10, 5.3, 5.13, 7.1, and 8.5 illustrate functions internal to the Apple IIe special purpose integrated circuits (the IOU, MMU, and timing HAL). These drawings are my own representations of those internal functions, based on my observations of Apple IIe signals and features. These drawings do not accurately show internal circuit detail, but are intended only to accurately depict internal circuit functions.

Understanding the Apple IIe is the result of an intensive investigation of the Apple IIe computer by the author. There is no other source of much of the information covered here, and the possibility of error exists on the part of the author. For those errors which do exist, the author is truly sorry.

The Apple IIe is not a perfect computer, Apple Computer, Inc. is not a perfect company, and I am not a perfect author. There are many opinions of the author in the body of the text, and some of them are negative toward the Apple IIe or the company that manufactures it. The reader must rely on his own judgment to evaluate these opinions. Although I am sometimes critical of Apple Computer, Inc., I acknowledge that the actions of this company have enriched my life. Although I am sometimes critical of the Apple IIe, I believe it is the best personal computer that money can buy.

# Contents

# Chapter 1—The Apple IIe—An Overview

APPLE He OVERVIEW 1-1 The Microprocessor and Bus Structure 1-2 Memory 1-3 Peripheral Slots 1-3 The Auxiliary Slot 1-4 The MMU, IOU, and Timing HAL 1-5 Video Output 1-7 The Keyboard 1-9 Other I/O 1-10 The Power Supply 1-11 SUMMARY 1-11

# Chapter 2-The Bus Structure of the Apple Ile

COMPUTER BUSES AND THREE STATE LOGIC 2-1 THE PIGEONHOLE COMPUTER 2-5 THE MPU, RAM, AND ROM 2-6 RAM ADDRESSING AND DATA DISTRIBUTION 2-7 ADDRESS DECODING 2-10 I/O (INPUT/OUTPUT) 2-14 THE COMPLETED BUS STRUCTURE 2-19

#### Chapter 3-Timing Generation and the

#### Video Scanner

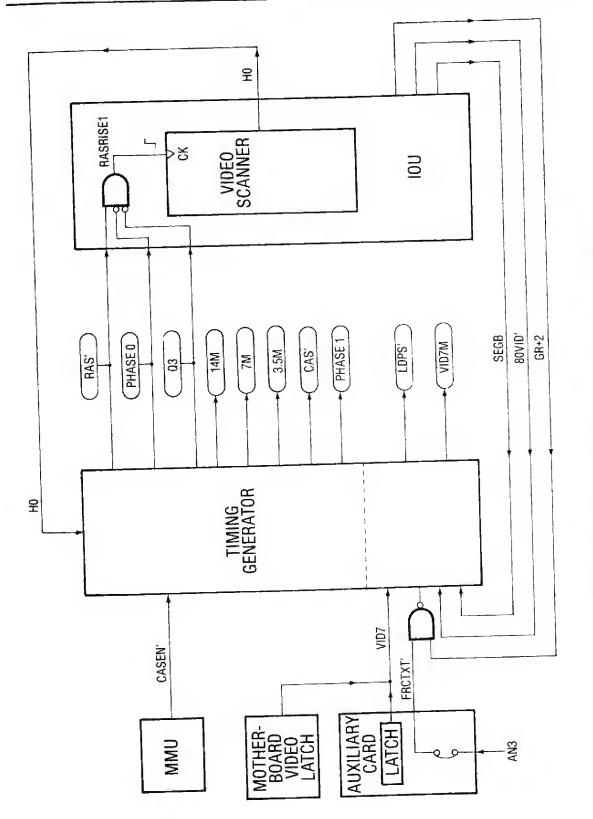

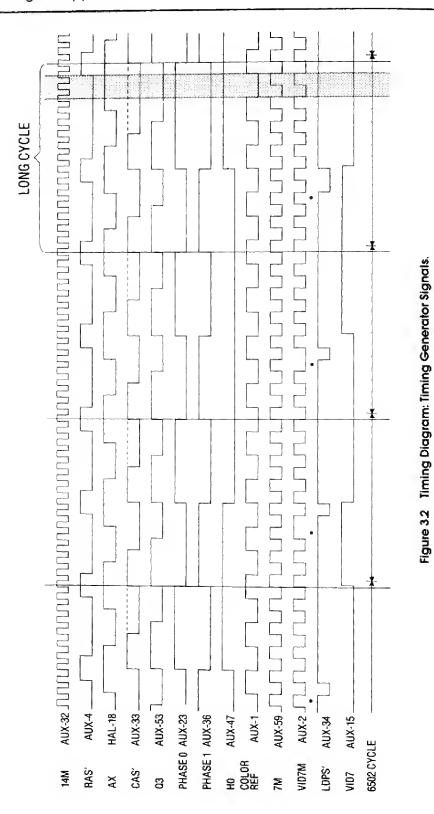

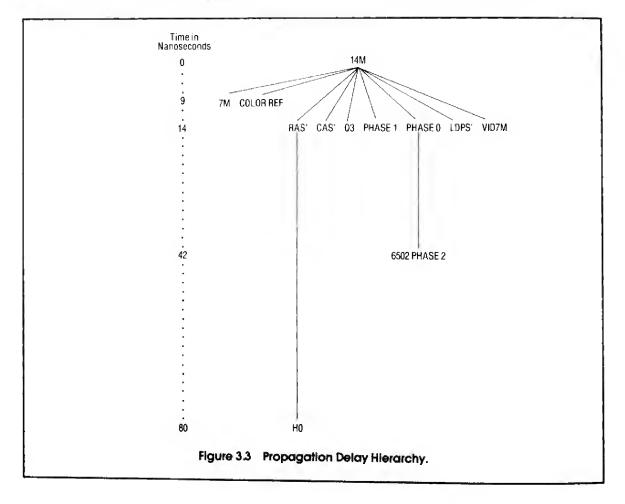

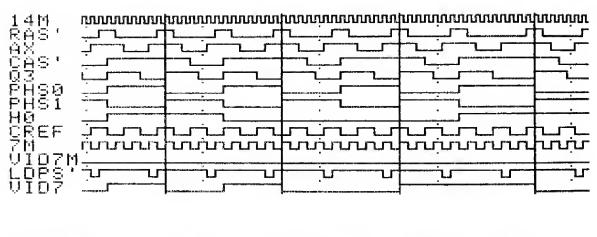

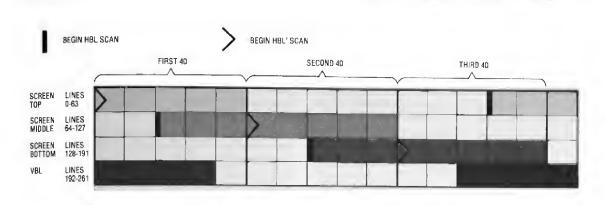

TIMING OVERVIEW 3-2 THE TIMING SIGNALS 3-2 APPLE FREQUENCIES 3-4 THE TIMING DIAGRAM 3-5 TIMING SIGNAL DISTRIBUTION 3-7 DETAILED DESCRIPTION OF TIMING SIGNALS 3-8 TELEVISION SCANNING 3-12 THE VIDEO SCANNER 3-13 THE LONG CYCLE 3-19 TIMING GENERATOR HARDWARE 3-19 APPLICATION NOTES Switching Screen Modes in Timed Loops 3-23 Apple Timing Loops 3-28 An Applesoft Emulator for the Timing HAL 3-29

#### Chapter 4-The 6502 Microprocessor

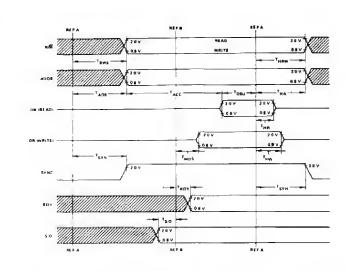

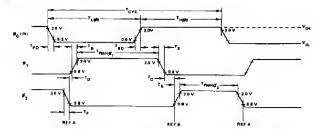

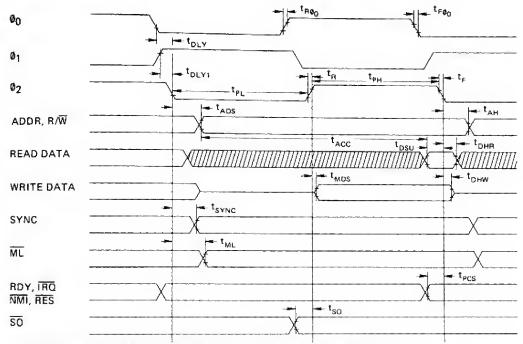

6502 SIGNALS 4-2 6502 CONNECTIONS IN THE APPLE IIe 4-4 6502 MEMORY USAGE 4-5 6502 TIMING IN THE APPLE IIe 4-5 APPLE PROGRAMMING 4-9 DMA IN THE APPLE 4-11 6502 INTERRUPTS IN THE APPLE IIE 4-14 RESET' 4-14 NMI' and IRQ' 4-15 The BREAK Instruction 4-17 The Enhanced Firmware IRQ'/BREAK Handler 4-18 Priority Among Interrupts 4-20 THE 6502 MICROPROCESSOR 4-21 APPLICATION NOTES 6502/65C02 Instruction Details 4-23 D Microflow Control Interval

D MAnual Controller 4-29

# Chapter 5-RAM and Memory Managemen

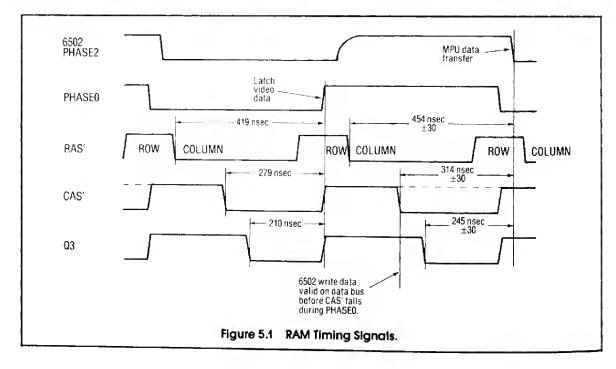

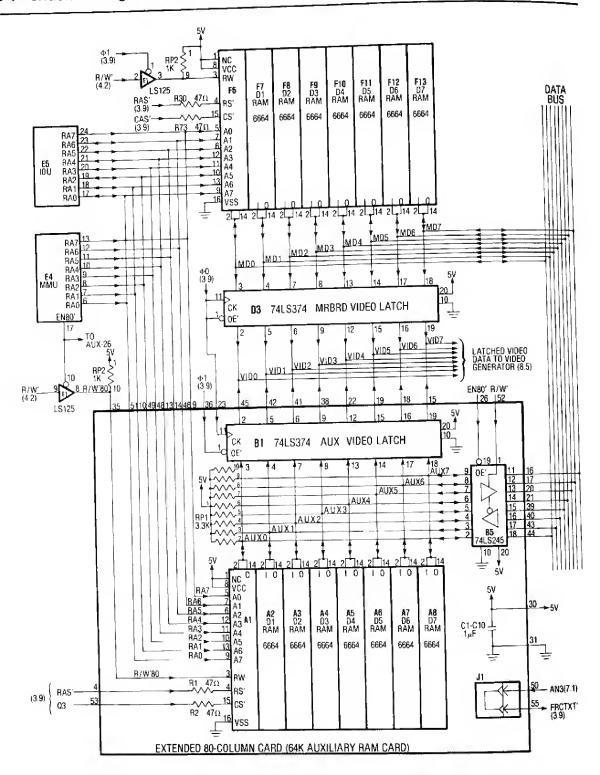

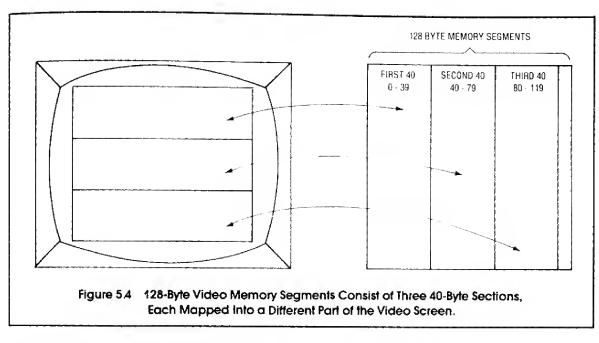

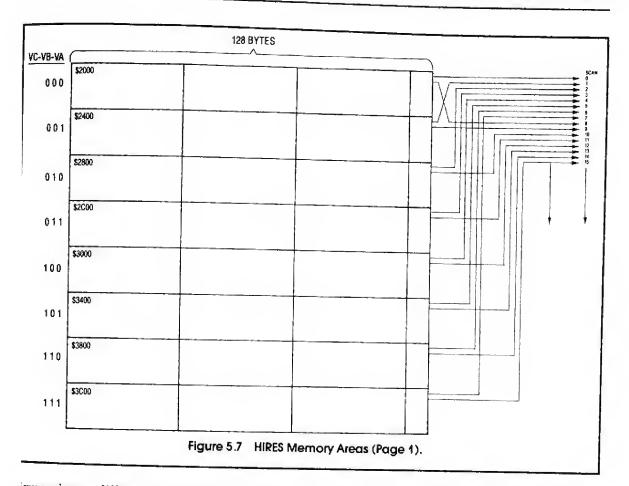

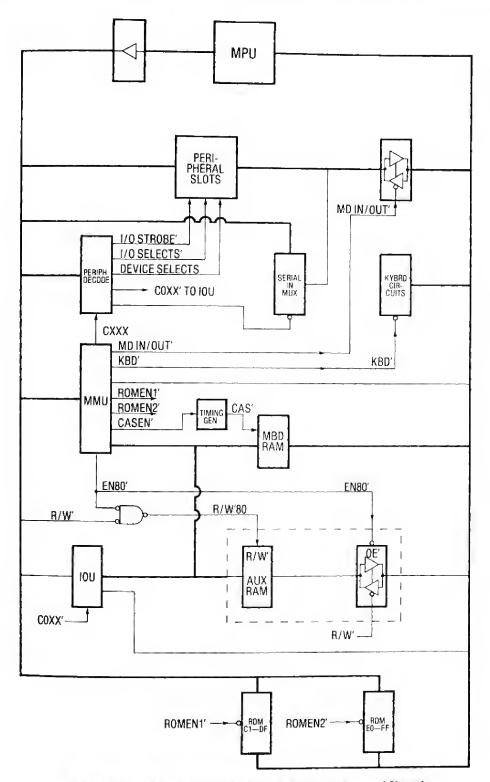

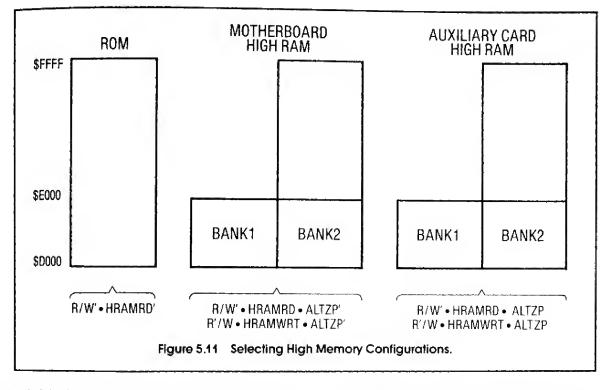

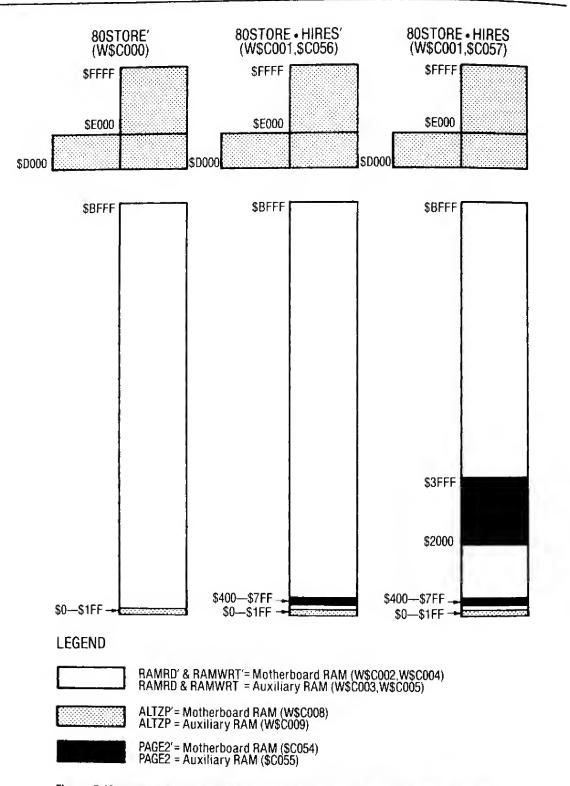

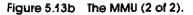

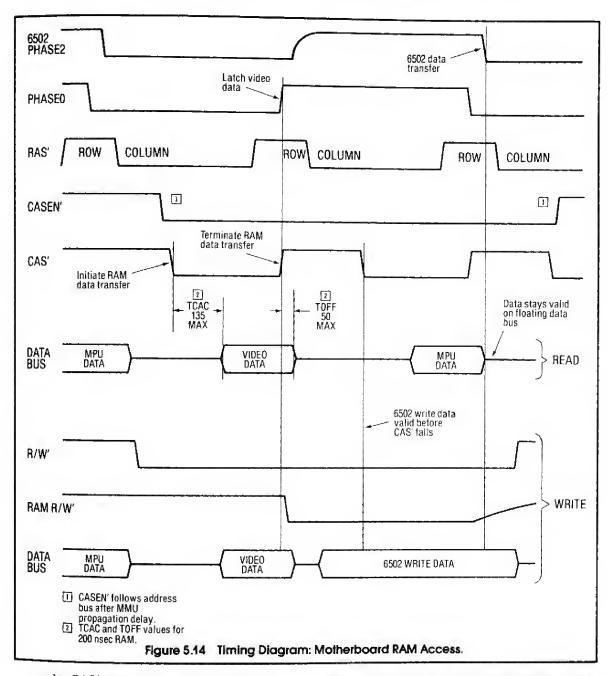

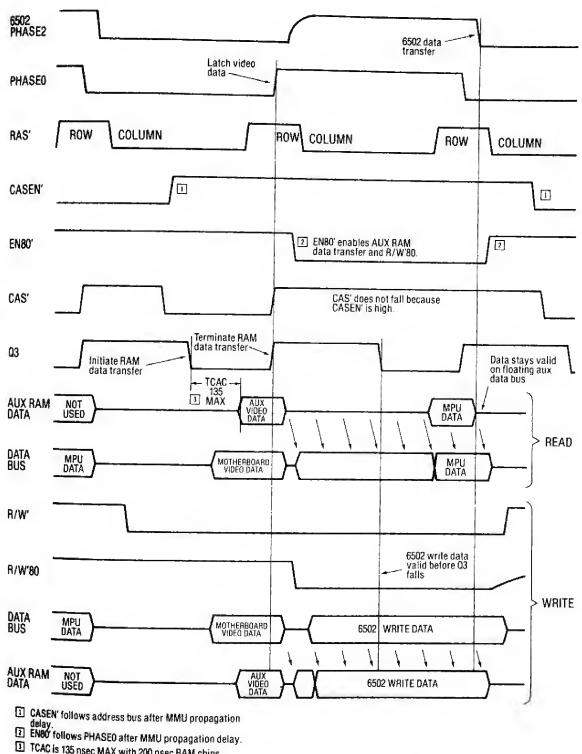

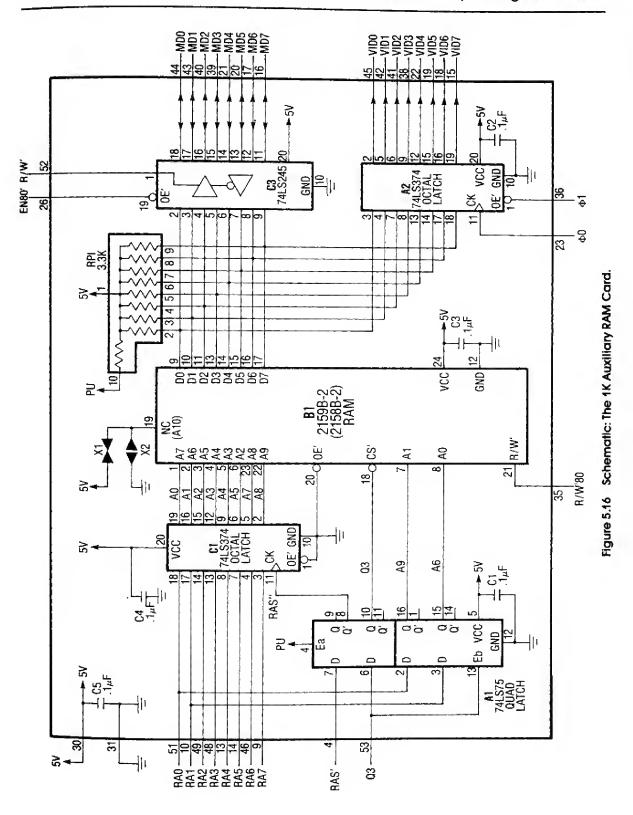

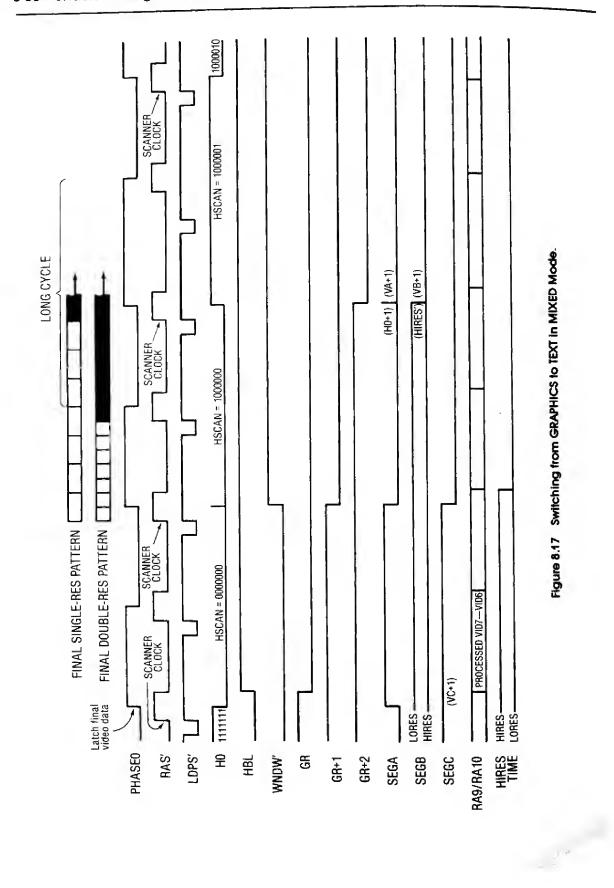

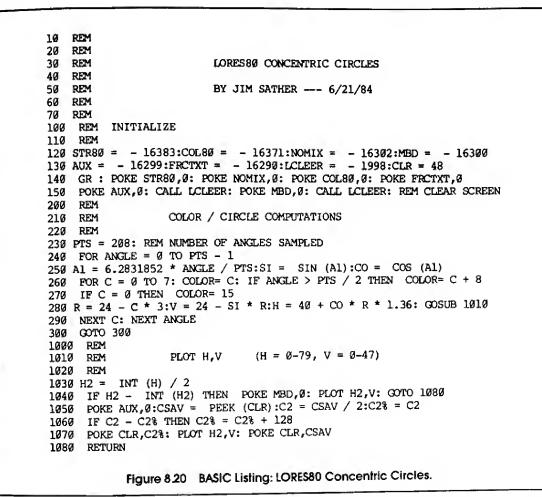

THE 64K DYNAMIC RAM CHIP 5-1 RAM CONNECTIONS IN THE APPLE IIe 5-3 RAM ADDRESS MULTIPLEXING 5-5 The Arithmetic of Video Scanner Memory Addressing 5-7 TEXT/LORES Scanning 5-10 HIRES Scanning 5-11 Mixed Mode Scanning 5-13 REFRESHING RAM IN THE APPLE He 5-19 MEMORY MANAGEMENT 5-20 MMU Soft Switches 5-20 Configuring High Memory (\$D000-\$FFFF) 5-20 Switching between Motherboard and Auxiliary Card RAM 5-24 Configuring the I/O Range (\$C000-\$CFFF) 5-28 KBD' and MD IN/OUT' 5-28 The MMU Functional Diagram 5-29 MMU Signal Propagation Delay 5-32 RAM TIMING IN THE APPLE He 5-32 THE 1K AUXILIARY RAM CARD 5-38 APPLICATION NOTES Reading Video Data from a Program 5-40

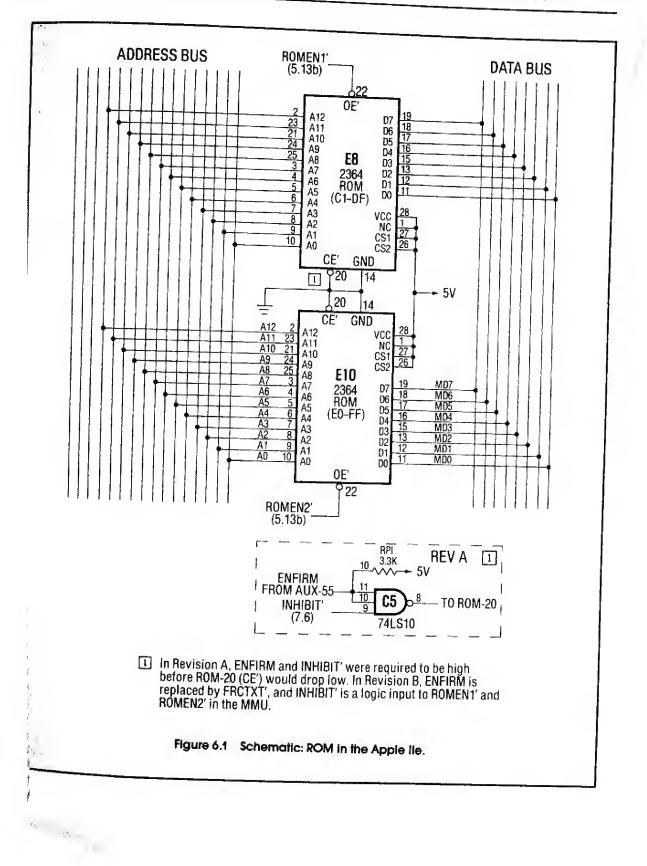

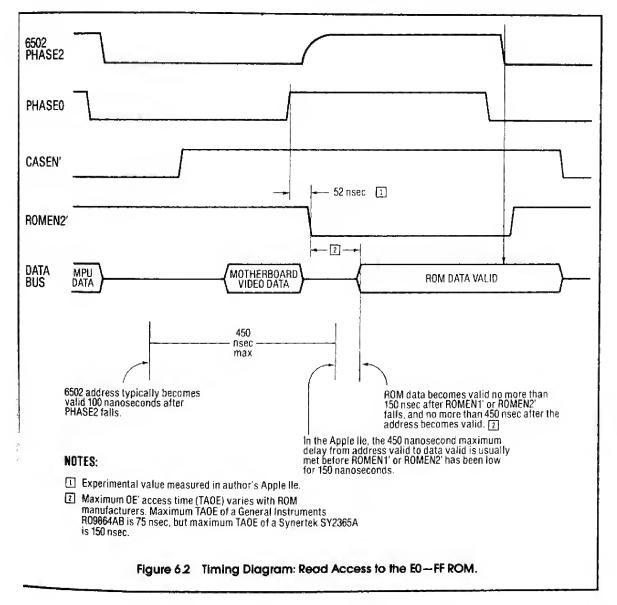

#### Chapter 6-ROM in the Apple lie

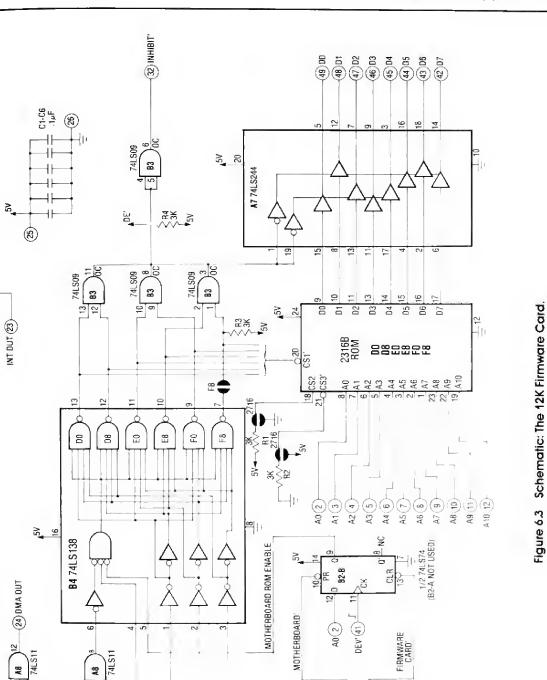

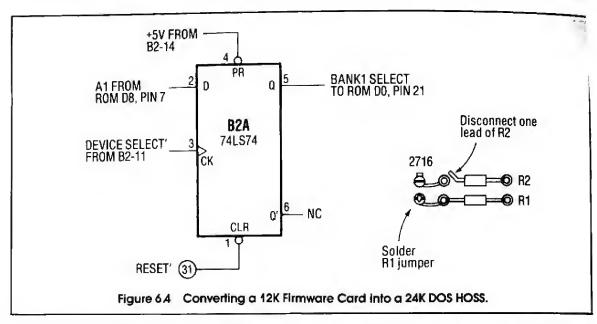

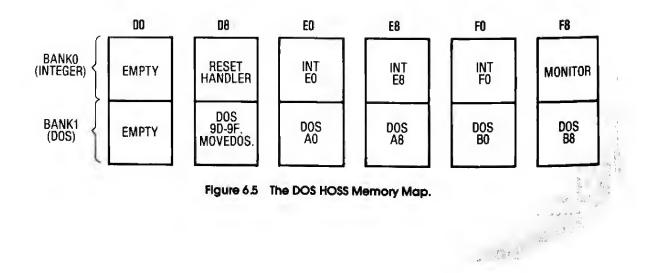

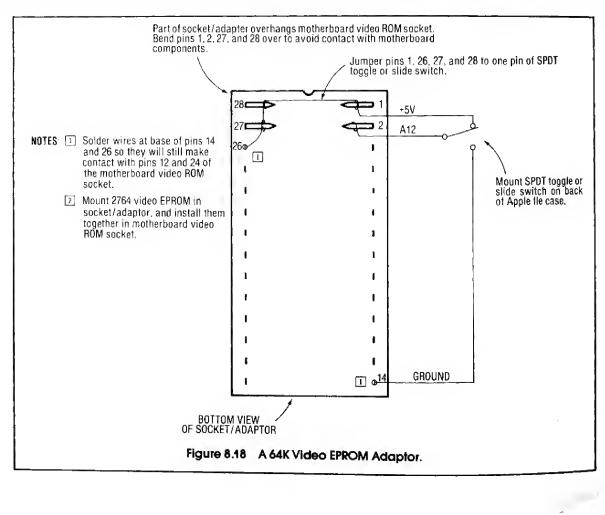

ROM HARDWARE 6-1 ROMEN1' AND ROMEN2' 6-2 PERIPHERAL SLOT ROM 6-4 ROM TIMING 6-4 FIRMWARE IN THE APPLE 6-6 The System Monitor 6-6 The Apple II Plus 6-7 The Impact of the RAM Card 6-8 The Apple IIe 6-8 The Apple IIe Firmware Upgrade 6-8 APPLICATION NOTES Modifying the System Monitor 6-10 Modifying a 12K Firmware Card into a 24K DOS HOSS 6-12

#### Chapter 7-Input/Output in the Apple lle

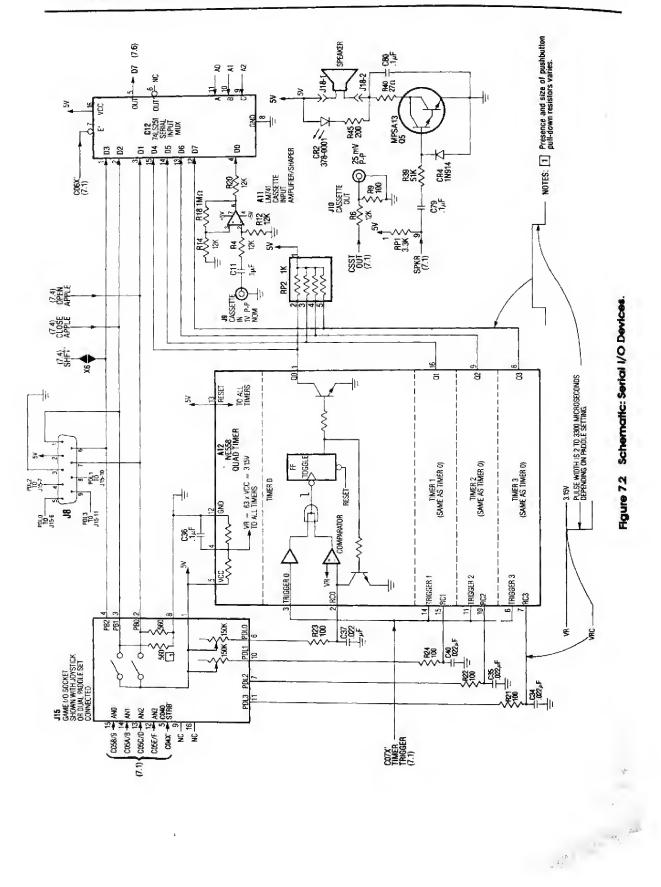

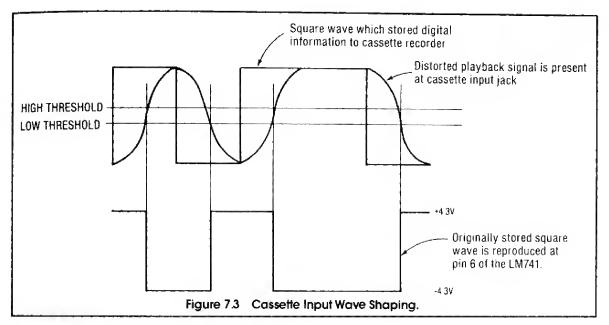

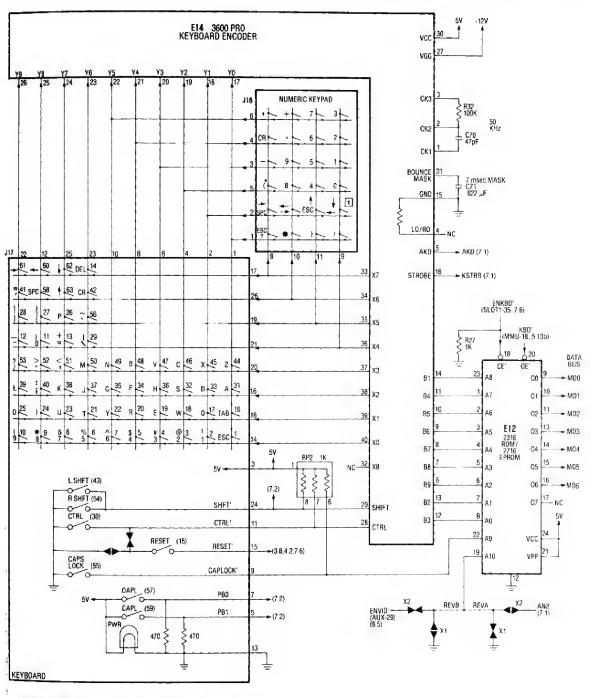

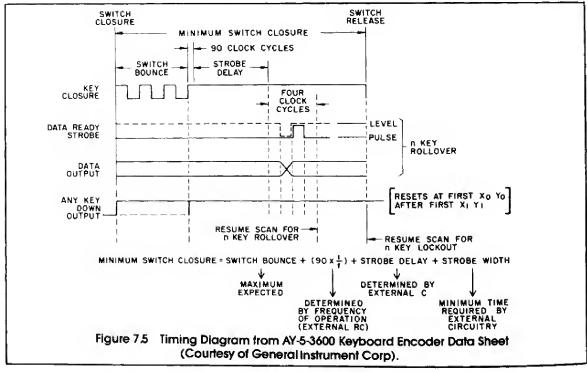

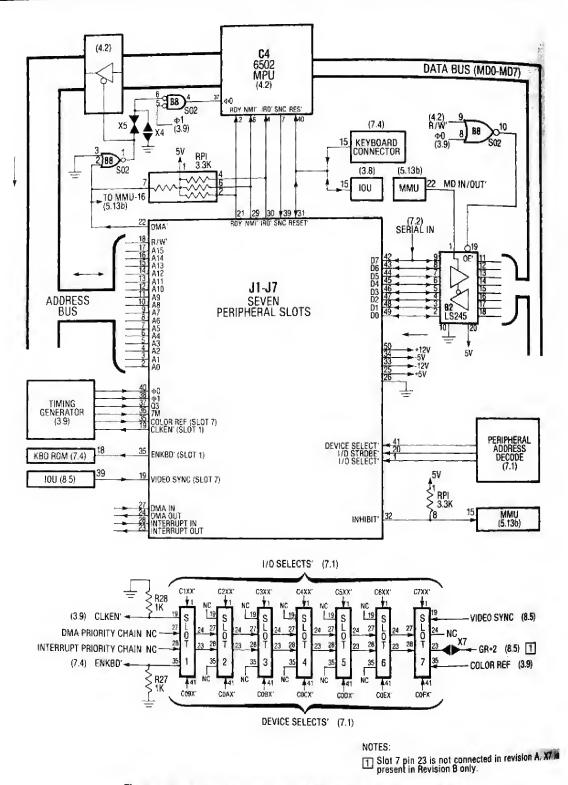

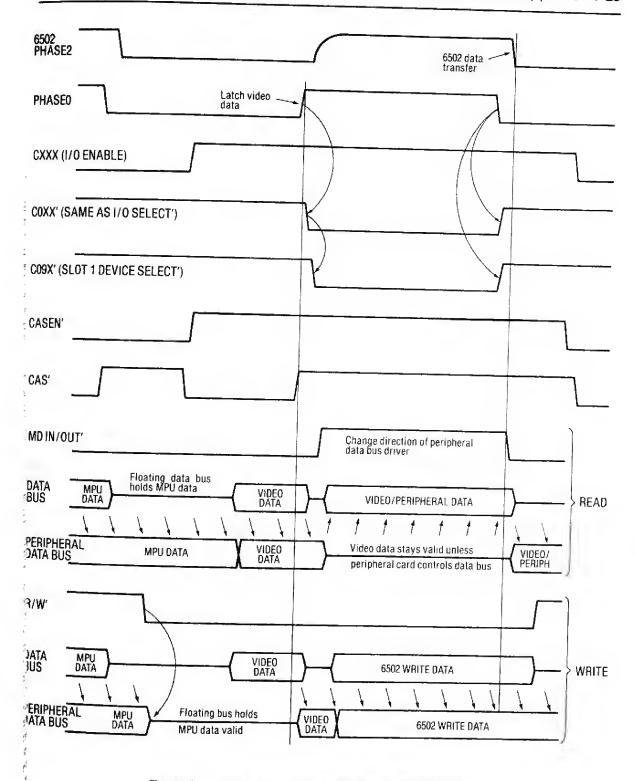

PERIPHERAL ADDRESS DECODING CIRCUITRY 7-1 IOU SOFT SWITCHES 7-3 SERIAL I/O HARDWARE 7-5 APPLE IIE KEYBOARD CIRCUITRY 7-9 PERIPHERAL SLOT CONNECTIONS 7-15 THE APPLE I/O SYSTEM: KSW AND CSW 7-21 Apple Monitor I/O 7-21 Linking I/O to Other Devices 7-22 Peripheral Cards and Primary I/O Devices 7-23 I/O TIMING 7-23 THE AUXILIARY SLOT 7-26 APPLICATION NOTES Programming the Game Paddles 7-29 Extending the Game I/O Socket 7-33 Gaining access to the Alternate Keyboard Set 7-37

94

# Contents

# Chapter 8-Video Generation

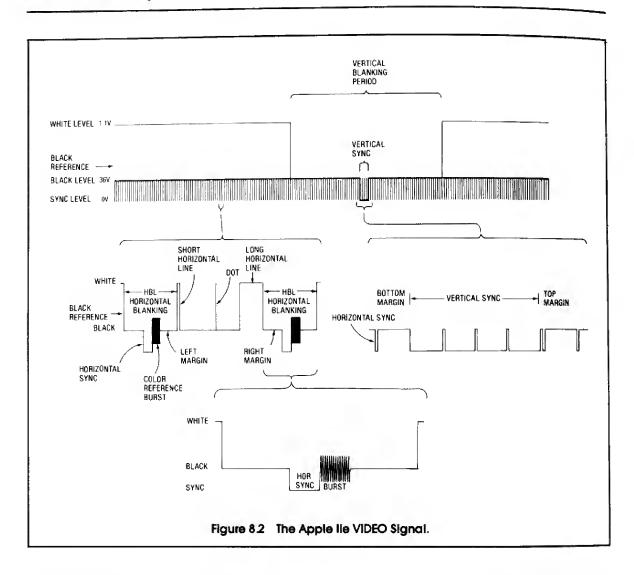

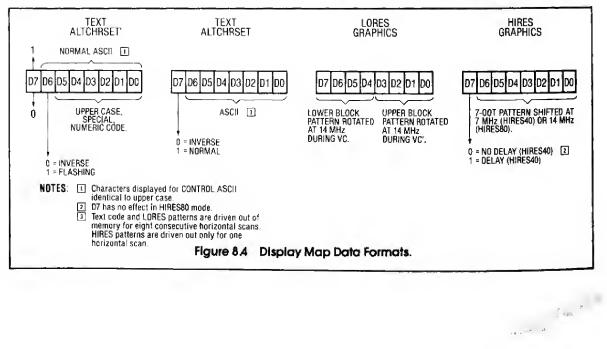

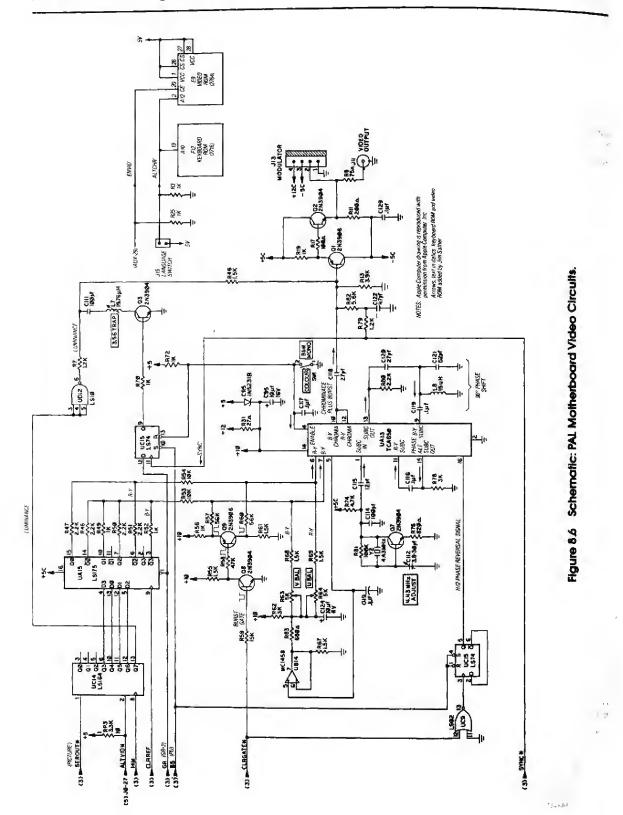

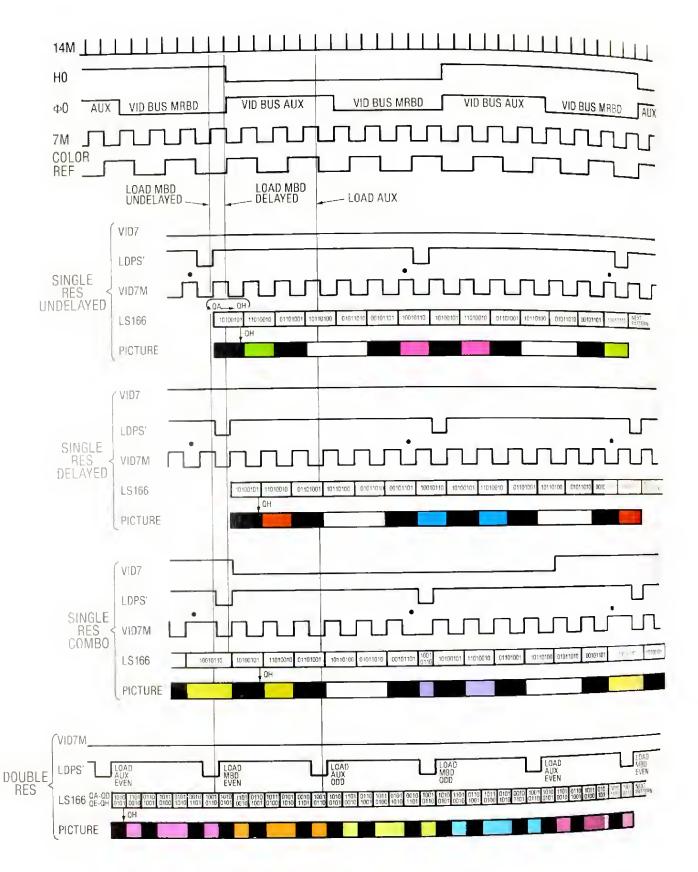

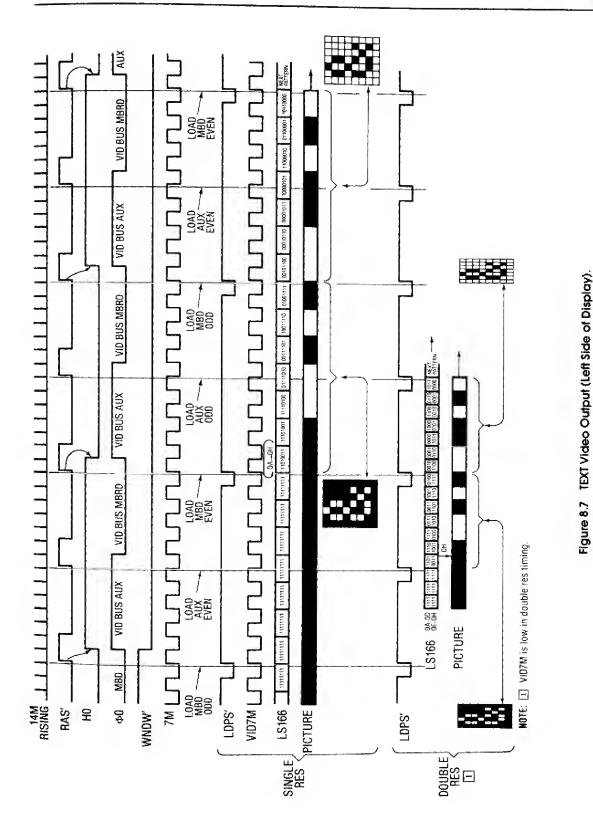

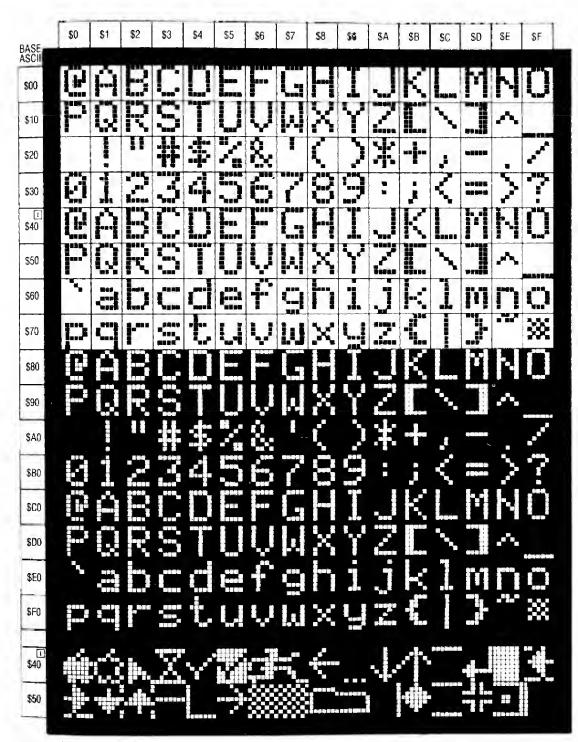

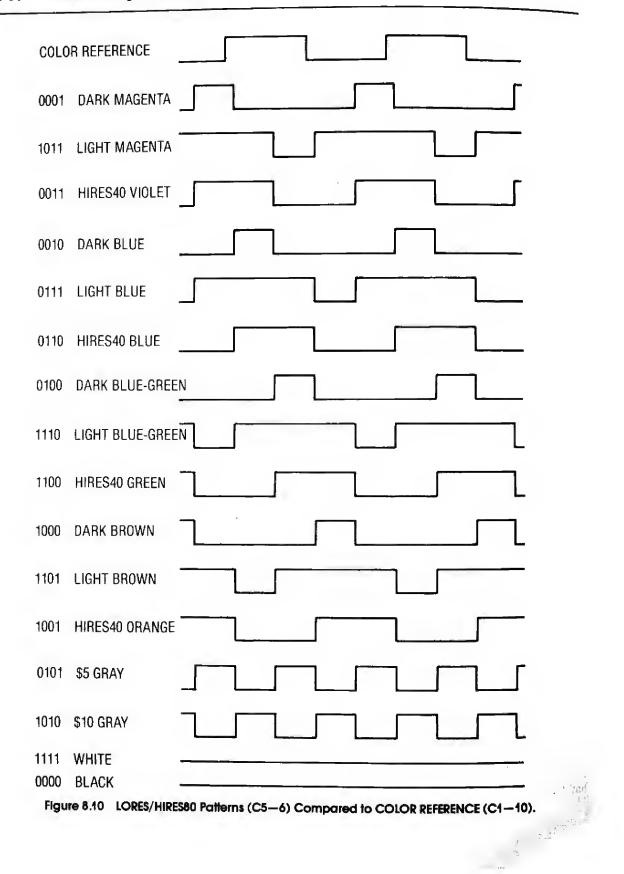

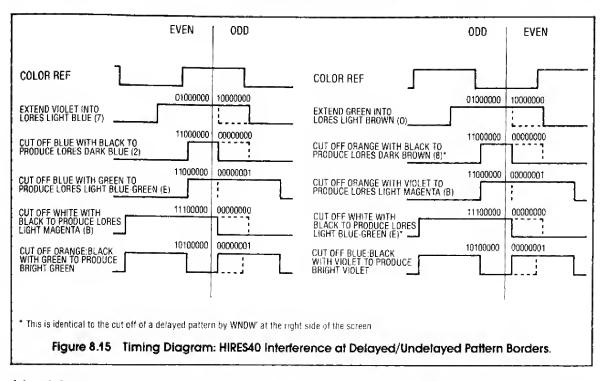

THE APPLE He VIDEO OUTPUT SIGNAL 8-3 COLOR SIGNALS 8-6 DISPLAY MAP MEMORY REPRESENTATIONS 8-8 VIDEO GENERATOR HARDWARE 8-9 Inputs to the Video ROM 8-11 Loading and Shifting of Dot Patterns 8-14 Loading and Shifting of Dot Patterns 8-14 Video Generation in Export Apples 8-16 DISPLAY MODE SOFT SWITCHES 8-19 VIDEO GENERATION TIMING SIGNALS 8-21 TEXT OUTPUT 8-24 LORES GRAPHICS OUTPUT 8-27 HIRES GRAPHICS OUTPUT 8-31 MIXED MODE SWITCHING 8-27 MIXED MODE SWITCHING 8-37 Programming Screen Character Sets in EPROM 8-40 Programming DOUBLE-RES Graphics Displays in BASIC 8-44 TECHNICAL NOTE

Details of Television Processing of Apple Video 8-47

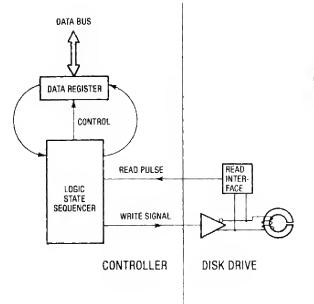

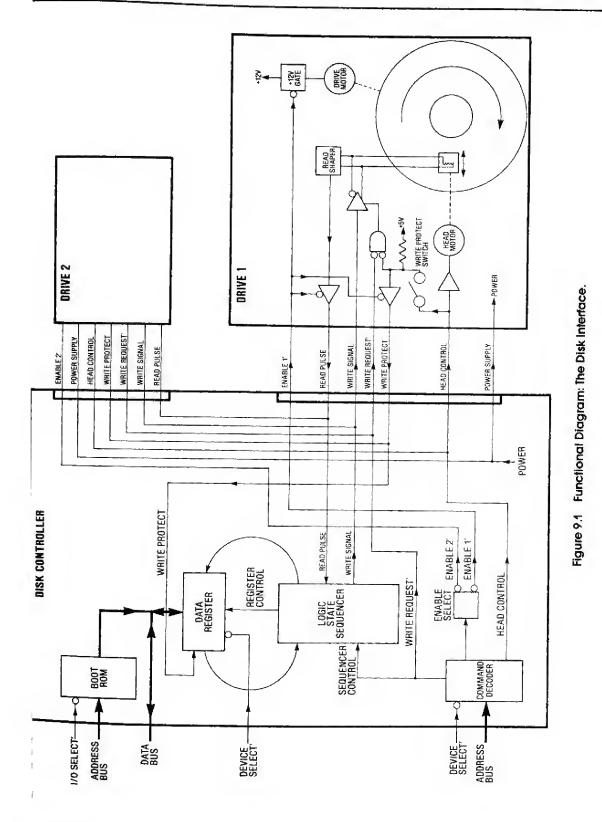

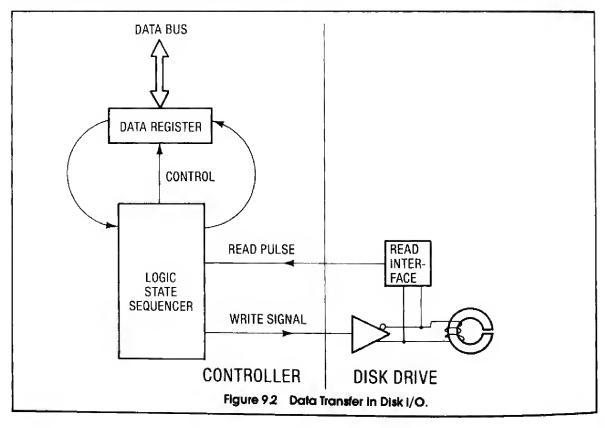

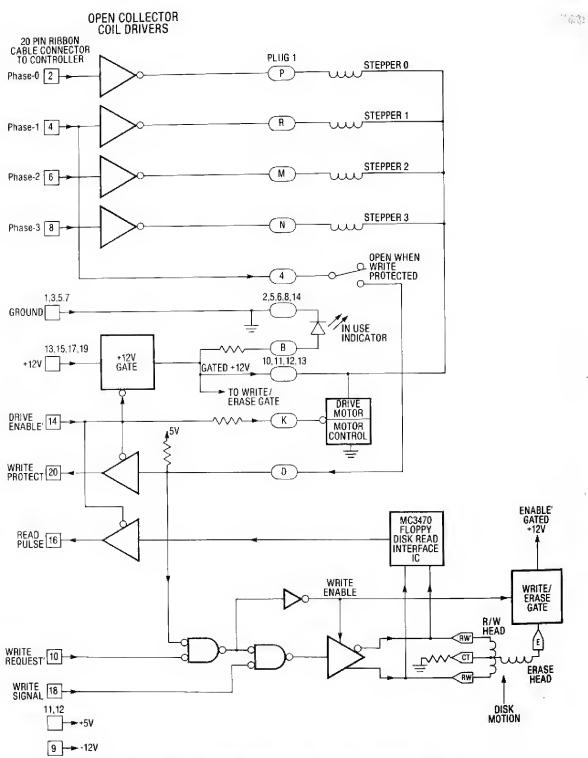

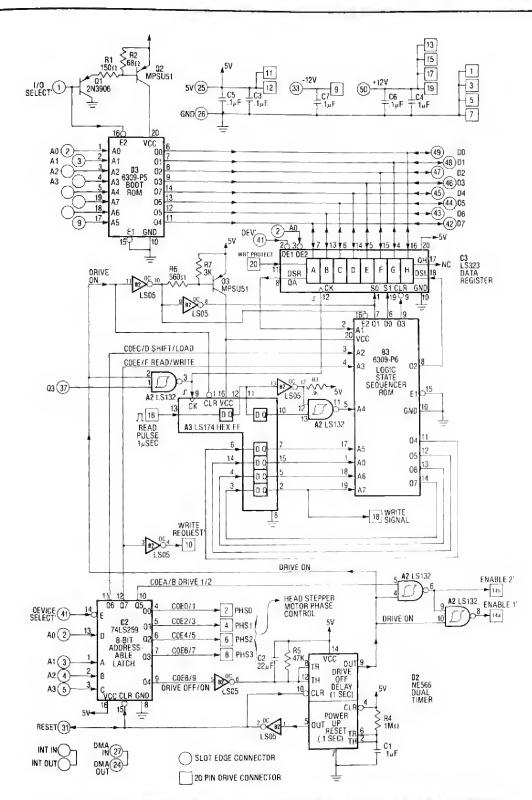

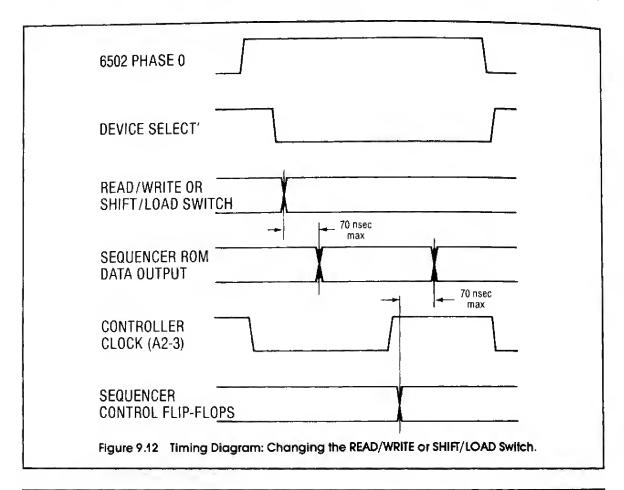

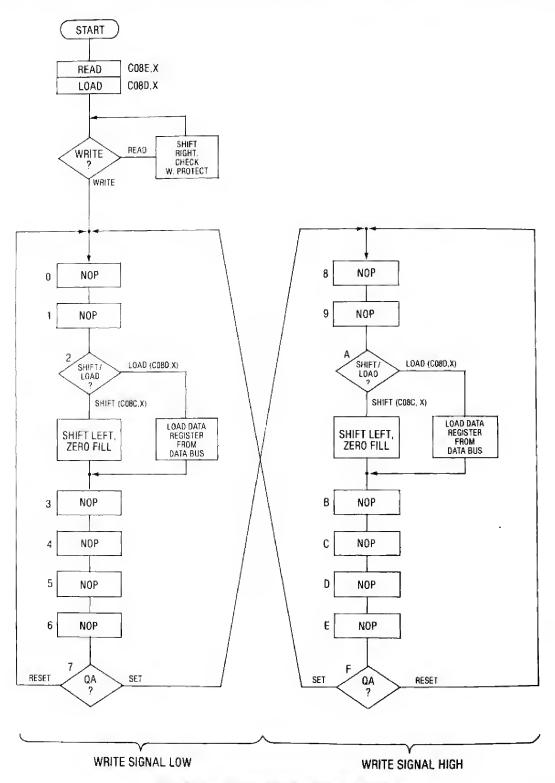

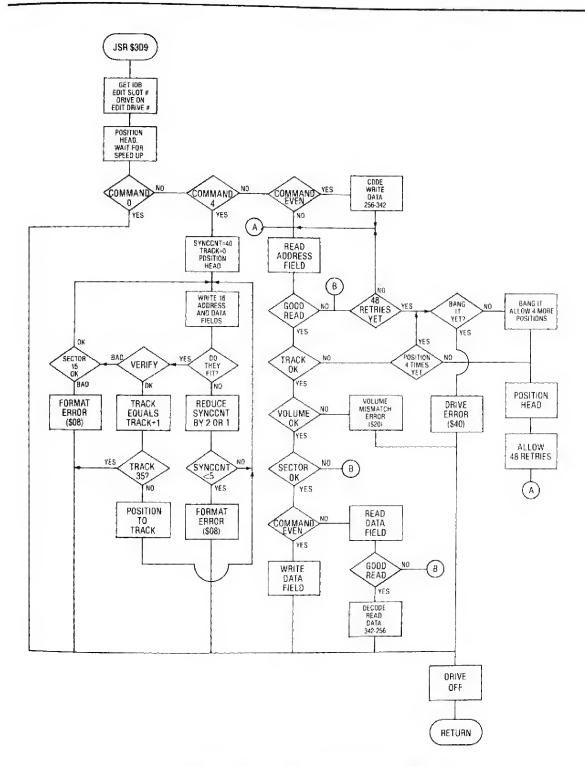

# Chapter 9-The Disk Controller

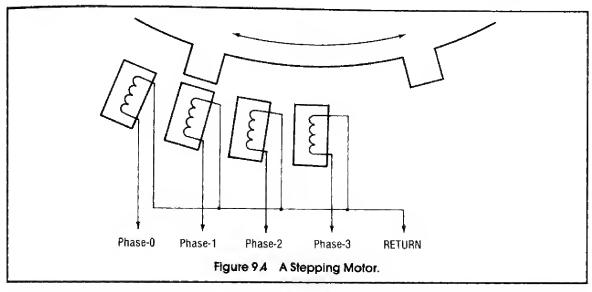

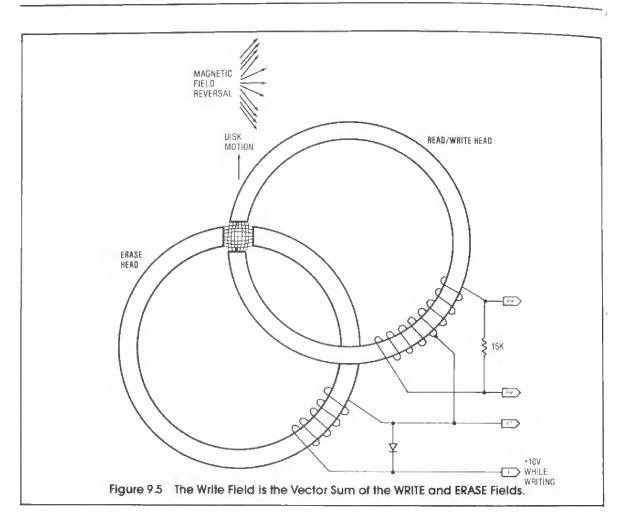

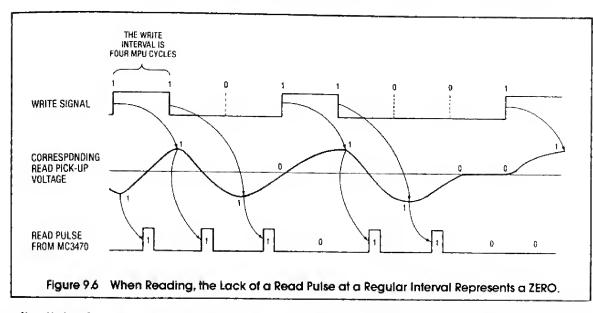

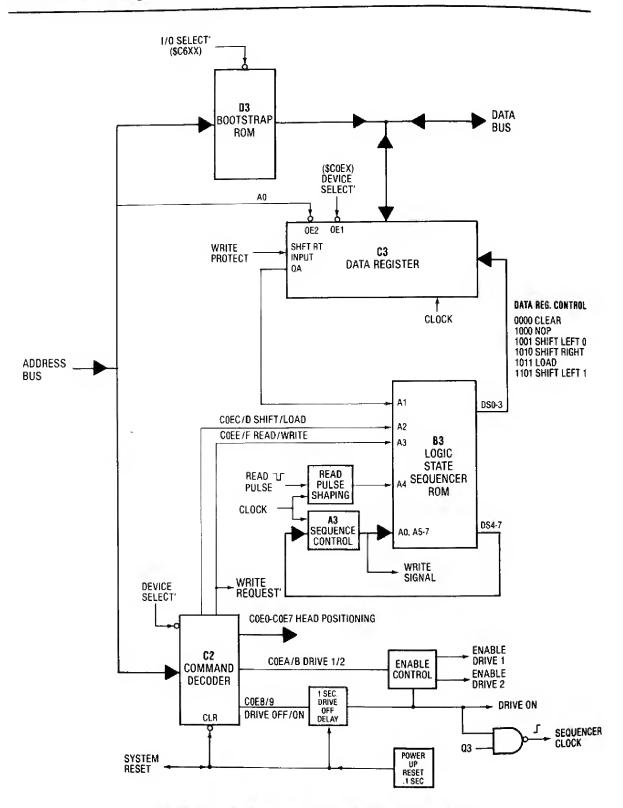

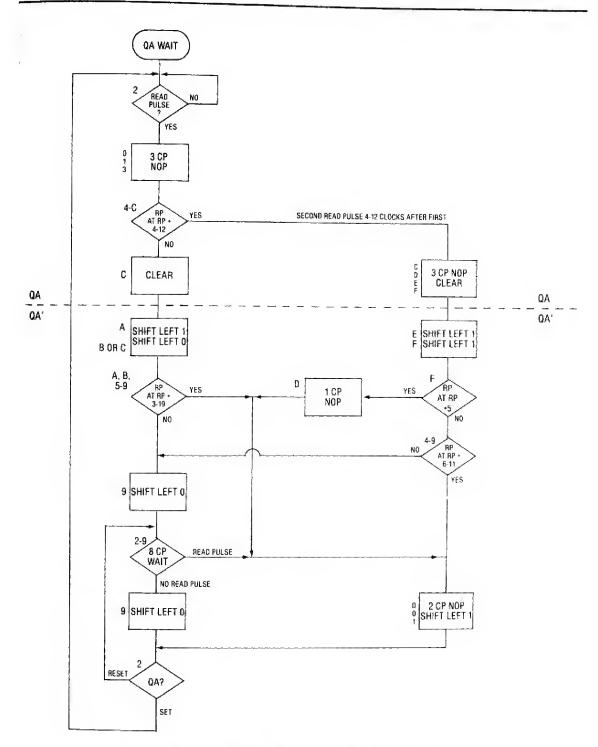

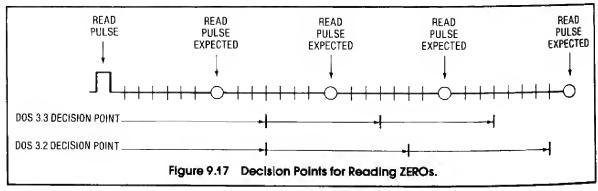

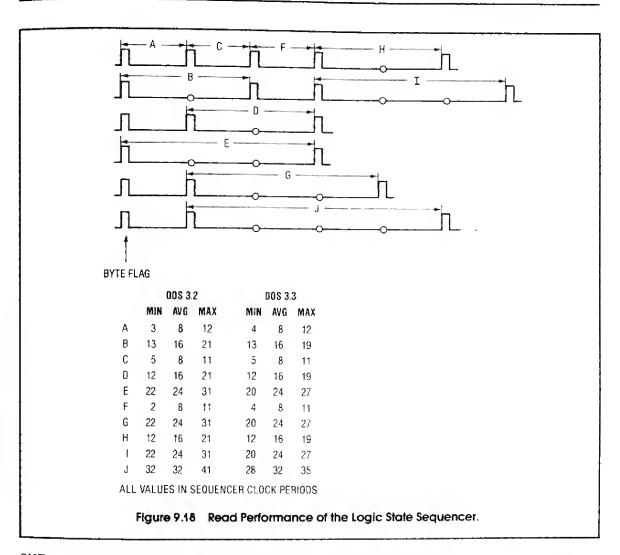

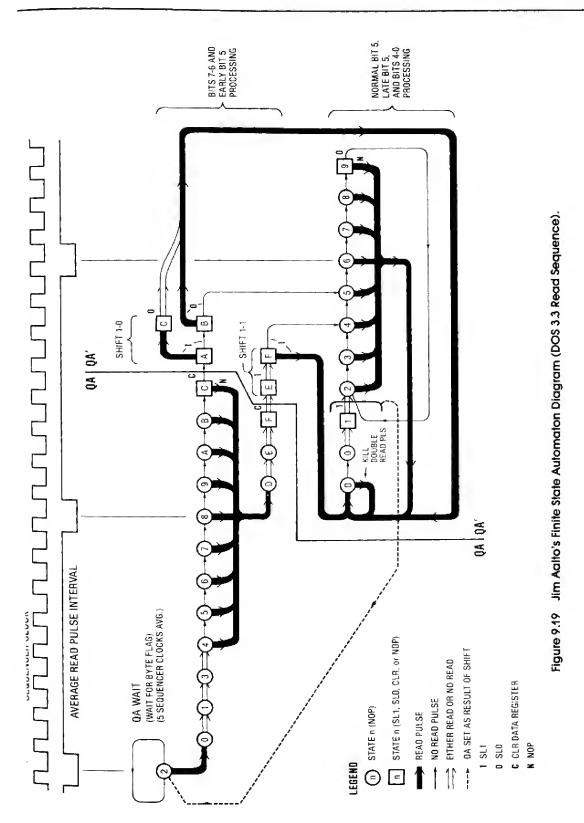

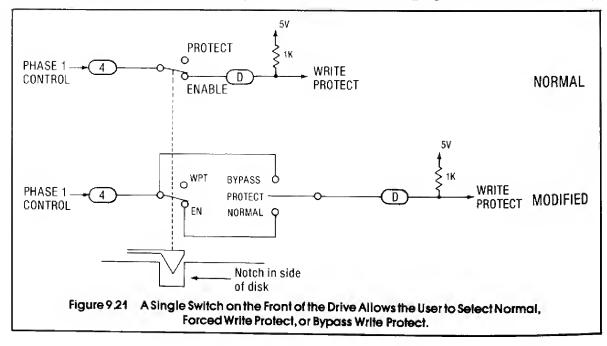

DISK II OVERVIEW 9-1 THE DISK II DRIVE 9-5 THE DISK II CONTROLLER 9-9 The Bootstrap ROM 9-9 The Command Decoder 9-12 Drive Off/On and Drive Select 9-12 Head Positioning Commands 9-13 READ/WRITE 9-13 SHIFT/LOAD 9-13 SHIFT/LOAD 9-13 The Logic State Sequencer and Data Register 9-14 The WRITE Sequence 9-21 The READ Sequence 9-27 PROGRAMMING EXAMPLES FROM RWTS 9-34 DIFFERENCES BETWEEN RWTS AND DIIDD 9-42 APPLICATION NOTE APPLICATION NOTE Installing a Write Protect Switch on the DISK II Drive 9-46

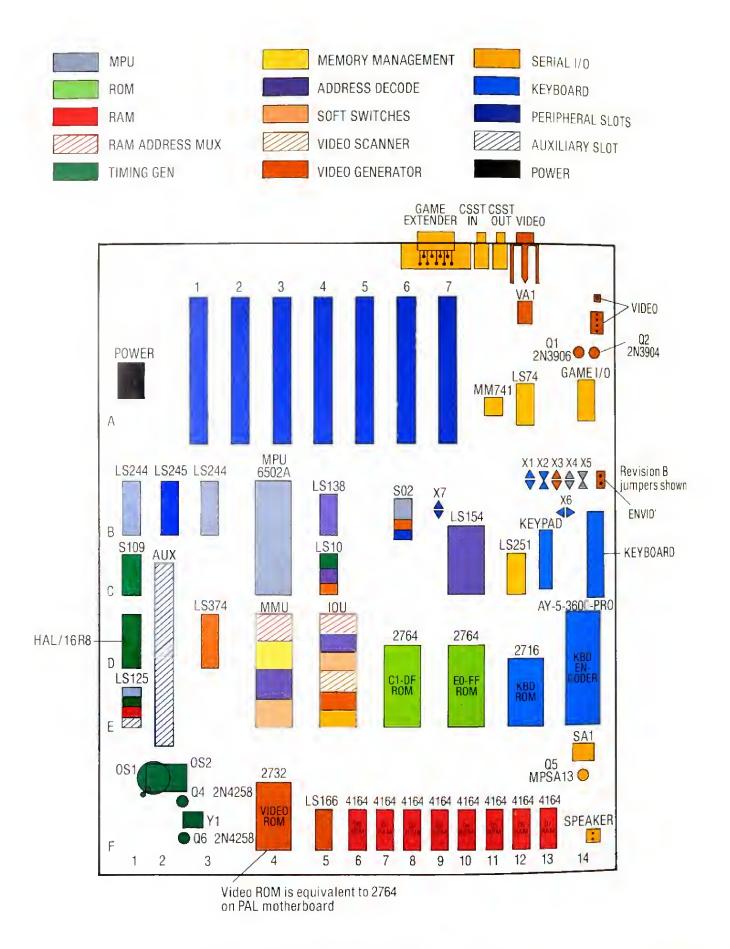

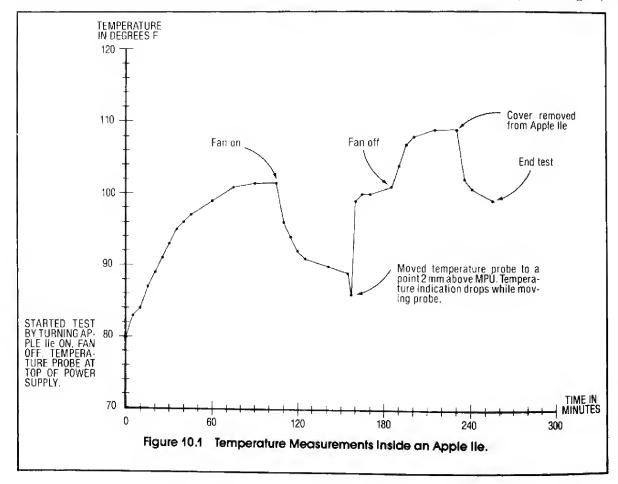

## Chapter 10-Maintenance and Care of the Apple lle

APPLE HARDWARE RELIABILITY 10-1 IMPROVING YOUR APPLE'S RELIABILITY 10-3 REPAIR OF THE APPLE IIe 10-4 WHEN YOUR APPLE BREAKS 10-6 The Firmware Diagnostics 10-6 The Peripheral Card Check 10-8 Power Supply Problems 10-8 Peripheral Failures 10-9 Other Symptoms 10-10

Glossary

Appendix A-References

Appendix B-Trademarks

Appendix C-6502/65C02 Data

Appendix D-BASIC Program Listings

Appendix E—A Logic Circuits Primer

Appendix F-A Number Systems Primer

Appendix G-Revisional Information

Appendix H—Historical Notes

Appendix I-Apple II/IIe Difference Notes

Index

#### Dedication

On behalf of my brothers and sisters, Lee, Jenny, Tim, Mary, Mike, and Joe, to my father, Fredrick Ingwald Sather, with love and respect.

#### Acknowledgements

My wife, Deborah, still tolerates me and proofreads all text before I submit it.

When I couldn't answer my own questions, I asked the telephone. Thanks for information, guidance, and answers to: Paul Darcy (PAL motherboard, history, general), Peter Baum (much general information and assistance), Pieter Lechner and Bob Sander-Cederlof (ProDOS), Walt Broedner (history), Dan Fischer (interrupts), Jeff Mazur (general), and Eric Waller, Roger Wilbur, and Mike England (maintenance procedures).

Every page of this book gives evidence of effort put forth by the people at Quality Software. What you see is far more polished than what I gave them.

### Note of Caution

Several of the Application Notes in Understanding the Apple IIe contain procedures for modifying the Apple IIe computer and peripheral cards. Modification of your Apple or peripherals may void your warranty if the warranty period has not yet lapsed. It may also increase your out of warranty repair costs should the modified unit fail in the future. The decision to perform any of the modifications described in Understanding the Apple IIe rests solely with the owner of the hardware concerned. Neither Quality Software nor the author bears responsibility for any negative consequence of the owner's decision to perform such modifications.

# chapter 1

# The Apple IIe— An Overview

The following overview is a brief statement of the hardware features of the Apple IIe computer. It is not meant to be a description of everything programs can make the Apple IIe do. Rather, it is a description of the basic capabilities with which computer programmers and peripheral designers work. An attempt is made to explain the technical terms that are used, but newcomers to microcomputers should not be discouraged if some points are not absolutely clear to them. The chapters that follow expand on all topics covered here, and Chapter 2 in particular contains information which will clarify much of Chapter 1.

First and foremost, the Apple II e is a revised and improved version of the Apple II computer that was designed by Steve Wozniak in the mid-seventies. It is operationally compatible with a 48K Apple II that has a 16K expansion RAM card in Slot 0 and an 80-column text card in Slot 3. The Apple II e also supports 64K of auxiliary RAM and has an improved keyboard, improved graphics capability, and numerous minor operational improvements, but compatibility with the Apple II is its predominant feature, Apple's motivation in refining the Apple II was reducing manufacturing costs and eliminating some critical text handling weaknesses of the Apple II. They achieved these goals very nicely and produced a computer that is better than the Apple II but which inherited its personality and many features from the Apple II. The computer that is described here is the Apple IIe, but much of what is said is also true of the Apple II.

#### **APPLE IIe OVERVIEW**

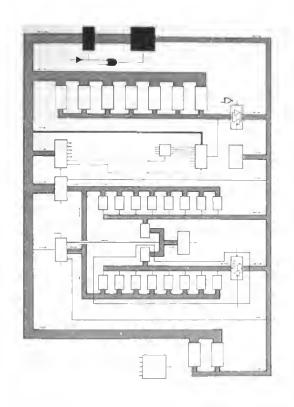

The Apple IIe is made up of five physical units: the baseplate and case, the keyboard, the power supply, the speaker, and the motherboard. The speaker, power supply and keyboard are all utility units which plug into the motherboard. It is the motherboard which contains all the uniqueness of the Apple IIe. The motherboard is the Apple IIe, and the Apple IIe is consequently referred to as a single board computer. On one board, it has a microprocessor, memory, video text and graphics output circuitry, seven peripheral expansion slots, an auxiliary expansion slot, and circuitry for communications with a variety of external devices. These features are part of an organized structure centered around the microprocessor.

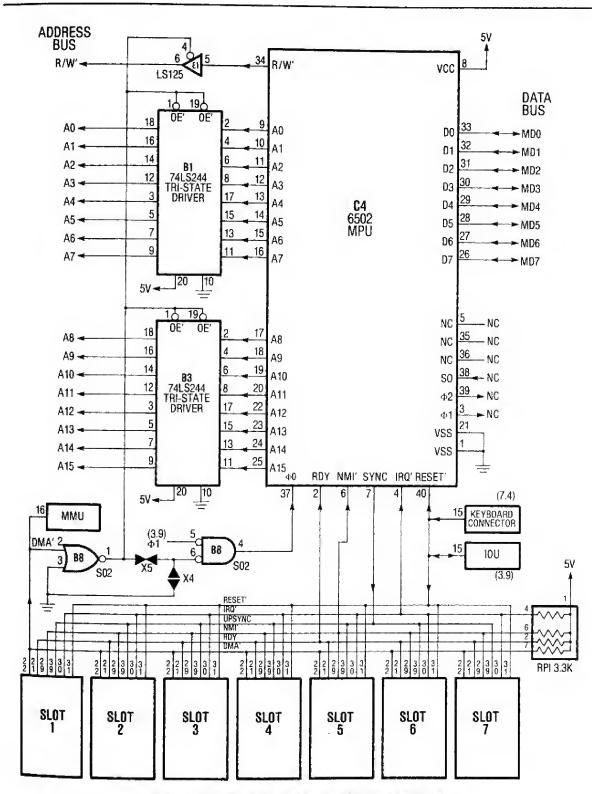

#### The Microprocessor and Bus Structure

The brains of the Apple IIe is a 6502 microprocessor. A microprocessor, or MPU (MicroProcessing Unit), is a single chip logic device capable of executing stored sequential programs.\* A microcomputer is a computer which uses an MPU as its fundamental logic processor.

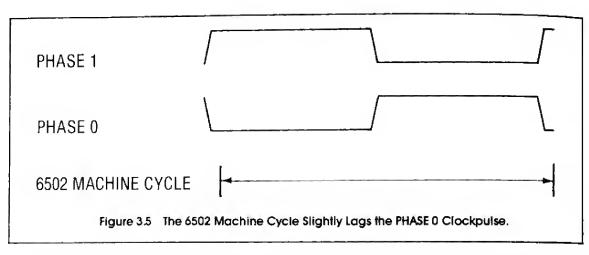

Digital computers operate to a synchronizing beat known as a clockpulse, similar to the beat of music, but over ten thousand times as fast. The 6502 operates to a beat which occurs approximately 1,020,500 times a second. We say that the clockpulse frequency is 1.0205 MegaHertz (MHz) meaning 1.0205 million cycles per second. Actually, there is a clockpulse jitter, which is described in the timing section of Chapter 3. Until we get to that point, just say that the 6502 operates at about 1 MHz. This, incidentally, is slow by modern microprocessor standards. There are 4 MHz 6502 MPUs available now, and other MPUs have faster clockpulse rates than that. With a given MPU, the faster the clock, the faster the execution speed.

The structure of the Apple IIe is that of multiple devices which can communicate with the MPU. Once every clockpulse, the MPU outputs the address of the location which is being communicated with, and it transmits data to or receives data from that location. The address which the MPU is putting out is distributed to all addressable devices in the Apple IIe via the address bus, and data is transferred between the MPU and the addressed location via the **data bus**. Associated and distributed with the address bus is the **read/write control output of** the MPU. Read/write control tells the addressed location whether data will be read from it or written to it.

The 6502 has 16 address outputs, each connected to one line (electrical conductor) of the address bus.\*\* It controls the 16 address lines and the read/write line together by placing a high or a low voltage on each line. The simultaneous condition of the 16 address lines is the 6502 address. The 6502 address is a number between \$0 and \$FFFF (65535), and the 6502 can access any one of the \$10000 (65536) addressed locations in that range.

The 6502 has eight data input/output lines, each connected to one line of the data bus. It controls the eight lines when writing and monitors the eight lines when reading, and the simultaneous condition of the eight lines is the 6502 data word. Like the address lines, each of the data lines is brought to a high or a low voltage when information is passed. Each line can be one of two states (high or low), so the information is said to be two state, or binary. Other common ways of referring to the two states of binary information are true/false, one/zero, and on/off.

A unit of binary information is a bit. Whether a line is high or low at a given instant is a bit of information. The 6502 reads or writes and manipulates information eight bits at a time and is therefore classified as an 8-bit MPU. A group of eight bits is a byte. The 6502 manipulates and transfers data, one byte at a time, to an addressed location in the Apple IIe bus system.

Most locations which the MPU addresses are memory locations. Memory contains the stored program which the MPU is executing and about half of the MPU's time is spent fetching that program. The program is stored sequentially, so fetching the program by the MPU simply involves incrementing the address output while reading the data input and interpreting it as a sequential program. When not fetching the program, the MPU is executing it. This execution involves logical manipulation of data, storage of data at or loading of data from addressed locations determined by the program, changing the program fetching location to somewhere other than the next sequential address, or any combination of these and other functions.

Not all locations addressed by the MPU are memory locations. Program instructions fetched from memory may cause the MPU to address nonmemory locations such as the speaker or keyboard. A memory location responds to a read at its address by placing data on the data bus. The speaker responds to a read or a write at its address with sound. The MPU thus controls the speaker via the address bus in an address decoding process.

<sup>\*</sup>A chip is another name for an integrated circuit, or IC. It is a unit with a small body and a number of metal pins or leads, and it contains complex electronic circuitry inside. If you look inside the Apple IIe, you will see many little black chips plugged into sockets on or soldered directly to the motherboard. There are four chips that are bigger than all the others, and the 6502 MPU is one of the four big chips.

<sup>\*\*</sup>As described in Chapters 2 and 4, the 6502 is not connected directly to the address bus. It is connected to the address bus through isolating devices which give the Apple IIe a DMA (Direct Memory Access) capability and allow the 6502 to address the large number of electronic devices connected to the address bus of the Apple IIe.

Address decoding is the only way a 6502 can control other devices, so all programmed control of Apple IIe devices is via address decoding.

#### Memory

General purpose microcomputers require two types of memory, memory you can change (RAM) and memory you can't change (ROM).\* RAM is necessary so you can store general programs and data. ROM is necessary so the computer has a program to run when it is first turned on.

Both ROM and RAM are random address memories, meaning any specific memory location can be accessed at its specific address. Computer memory is like thousands of light bulbs, each of which may or may not be glowing. If the memory is random access, the microprocessor can communicate with any light bulb it chooses by calling its number. It can, for example, check if light bulb number 25,765 is glowing or not. This is analogous to reading from memory. Telling light bulb number 7,682 to not glow is analogous to writing to memory; the MPU is altering the state of light bulb 7,682. RAM and ROM are functionally identical except that ROM is fixed as if it was etched in stone. You can't turn the light bulbs on or off. You can only check to see if they are on or off.

The MPU cannot really tell whether a light bulb is glowing or not, but it can tell whether the voltage on a line is high or low. RAM is capable of storing the high/low state of its data input when the MPU writes data to a RAM address. Both RAM and ROM are capable of bringing their data outputs high or low in accordance with stored data when the MPU reads data from a RAM or ROM address. In a positive logic system like that of the Apple IIe, storing or reading a high voltage is thought of as storing or saving a "1". Storing or reading a low voltage is thought of as storing or saving a "0".

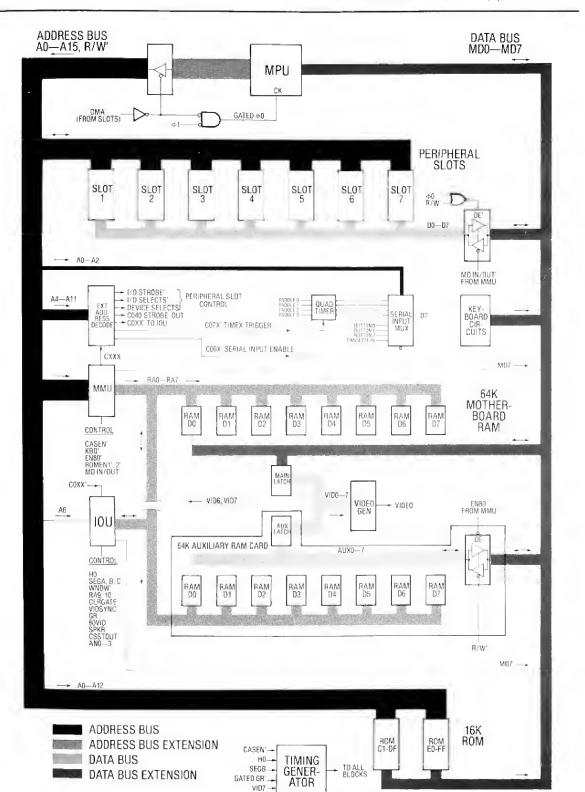

Since the 6502 is an 8-bit MPU, memory must be organized so that it is accessed eight bits, or one byte, at a time. The Apple IIe motherboard has sockets for 65,536 bytes (524,288 bits) of RAM. This is normally referred to as 64K of RAM, meaning 64 Kilobytes. In addition to this motherboard RAM, motherboard timing and memory management fully support an additional 64K of RAM on a card

n - Usiy - and

installed in an **auxiliary slot** that is mounted near the front of the motherboard.

The 64K of motherboard RAM in the Apple He is functionally similar to the 64K of RAM in an Apple II with Slot 0 16K expansion RAM card. Low RAM is the 48K addressed at \$0000-\$BFFF, and high RAM is 16K addressed at \$D000-\$FFFF with \$D000-\$DFFF response switched between two 4K banks. Low RAM is the main body of Apple IIe RAM, and it does not share \$0000-\$BFFF with other motherboard devices. High RAM is secondary RAM that shares \$D000-\$FFFF response with motherboard ROM. It is disabled for reading, in favor of motherboard ROM, anytime the RESET key is pressed. Auxiliary card RAM is divided the same way as motherboard RAM, so a 128K Apple He is the RAM equivalent of two 48K Apple Hs with two 16K RAM cards.

The Apple IIe uses dynamic RAM which must be refreshed. Memory refresh must occur on a periodic basis or dynamic RAM will not work. It's like a fire that goes out unless someone is constantly pumping the bellows. Dynamic RAM is nice because it's inexpensive, but it requires a lot of external circuitry to support the refresh requirement. The Apple IIe fully supports 64K of motherboard RAM and 64K of auxiliary card RAM in every way, including refresh.

The Apple IIe motherboard contains 16,128 bytes of system firmware (programs and data in ROM). This firmware includes a system monitor, Applesoft BASIC, some separate keyboard-in / video-out routines referred to as the 80-column firmware, and some system diagnostic routines. The monitor tells the Apple IIe what to do at power-up and contains valuable utilities which make the Apple IIe hardware accessible to its user; Applesoft is the BASIC editor and command interpreter normally used in the Apple IIe; the 80-column firmware is an extension of the monitor written to support the Apple IIe 80-column text display; and the firmware diagnostics provide the Apple IIe with a modest self testing capability.

#### Peripheral Slots

The Apple IIe peripheral slots are similar to a card cage. What is a card cage? A card cage is a very versatile physical package for microcomputers and other electronic circuits. It is a row of slots mounted close together into which printed circuit cards are plugged. Behind the slots are hundreds of wires connecting the slots together in accordance with the design purpose. Card cage architecture is

<sup>\*</sup>ROM stands for Read Only Memory, which is accurate, and RAM stands for Random Access Memory, which is the most famous misnomer in all of computer jargon. Both read only memory and read/write memory in the Apple IIe are random access memory, and this book refers to them by their conventional labels. ROM and RAM.

like a house with an intercom system. Just as communication is possible between various rooms of the house, communication is possible between the various cards plugged into the card cage. Each slot in the card cage is a different station in the intercom system.

In a card cage microcomputer, part of the wiring which interconnects the slots is a multiline address bus and data bus, similar to the buses on the Apple Ile motherboard. A microprocessor board can be plugged into any slot, from where it can control communication in the card cage via the address bus. A very nice modern card cage micro would have a multifunction single board microcomputer in one slot and a variety of devices in the other slots. The Apple IIe is exactly that computer, turned inside out. Instead of mounting the main logic board in the card cage, they mounted the card cage on the main board.

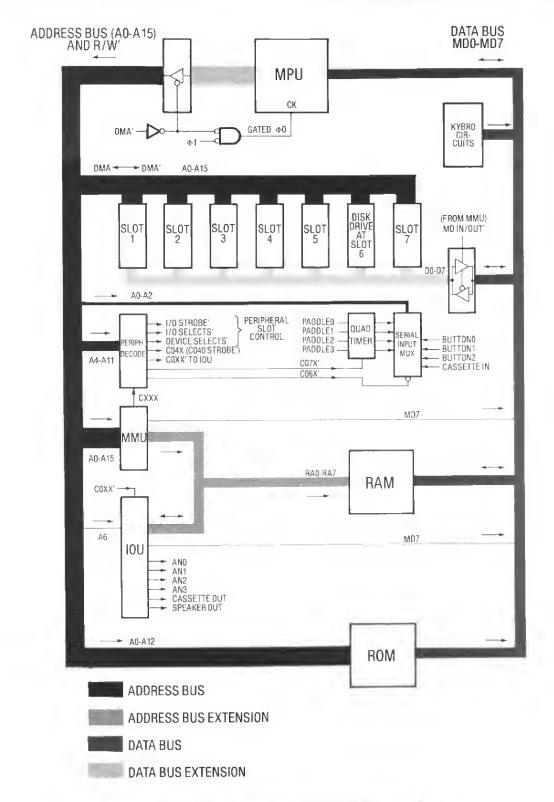

The Apple IIe "card cage" consists of seven peripheral slots mounted on the back of the motherboard. The address bus and data bus are connected to all the slots, making them addressable extensions of the Apple's basic communication system.\* Each slot has a part of the 6502 address range assigned to it, so programs can make the 6502 access a peripheral slot just as if it were a group of memory locations.

Some important 6502 input control signals are tied to pins on the peripheral slots. They are RESET', READY, NMI' (Non-Maskable Interrupt), and IRQ' (Interrupt ReQuest). These signals are all described in greater detail in the 6502 section of Chapter 4. Their connection to the peripheral slots means that the processor can be interrupted, stopped, started, and reset from any peripheral card. It also means that any peripheral card can be designed to respond to these control signals. For example, pressing RESET at the keyboard resets the 6502 and additionally turns off the floppy disk drive. The disk drive controller is designed to respond to the RESET' signal which is pulled low when RESET is pressed. RESET', incidentally, is read "reset prime." In this book, the prime behind the name of a logic term is used to signify that a signal is active or true when a low voltage is present.\*\* It is an aid to understanding the logic functions of a given signal. Knowing this, you could guess from the second sentence of this paragraph that the 6502 is interrupted and reset by low voltages on the NMI', IRQ', and RESET' lines, and enabled by a high voltage on the READY line.

Another peripheral slot signal which affects the 6502 but isn't connected directly to it is the DMA' signal. DMA stands for Direct Memory Access and refers to direct memory access from the peripheral slots. The DMA' line does a bit more than give the slots access to memory, however. It allows a card in a slot to isolate the 6502 from the address bus and data bus and take control of communication in the bus system. This means that a peripheral card can control all hardware features of the Apple IIe. It is as if you could plug a Suzy brain into Johnny and have the Suzy brain control Johnny's body, a concept much in vogue in some circles.

There are signals connected to the peripheral slots other than those that have been mentioned. They provide various capabilities so peripherals can be designed to be fully integrated into the Apple structure. These signals include timing and control inputs, power supply voltages, and control signals decoded from address ranges on the address bus. The purposes of these signals will be fully explained in later chapters.

#### **The Auxiliary Slot**

The auxiliary slot is a 60-pin slot that is physically separated from the peripheral slots. Like a peripheral slot, the auxiliary slot holds a card that is designed to augment the features of the motherboard. Unlike a peripheral slot, the auxiliary slot does not feature full connection to the address bus and data bus and is not supported as an I/O port by Apple IIe firmware.

Rather than acting as an I/O port, the auxiliary slot is designed to accept cards that interact with the RAM, video generation, and/or timing generation circuitry of the motherboard. It most commonly holds a 64K RAM card that enables video display of 80-columns of text, enables doubling of the Apple IIe video graphics horizontal resolution, and makes a total of 128K of RAM accessible to the Apple IIe MPU. Other functions such as RGB (Read-Green-Blue) video signal generation can also be performed

<sup>\*</sup>As described in Chapters 2 and 7, the peripheral slots are actually connected to the data bus through a bidirectional bus driver that enables the 6502 to communicate with a large number of peripheral card devices via the data bus.

<sup>\*\*</sup>Most published computer literature will overscore a logic term, rather than placing a prime symbol behind it, to signify that it is active when low. In using the prime notation, Understanding the Apple IIe is following the convention used by Apple in the Apple IIe Reference Manual for IIe Only. In addition to signifying that a term is active when low, the prime symbol following a logic term can mean that the inversion of that logic term is being referred to. Please see Appendix E for further discussion of this subject.

by auxiliary slot cards, but such alternate function cards will probably always contain at least enough RAM to support the Apple IIe 80-column text display. Additionally, production and service facility auxiliary slot cards can be designed to monitor important Apple IIe timing and video generation signals and inject substitutes for many of those signals to the motherboard.

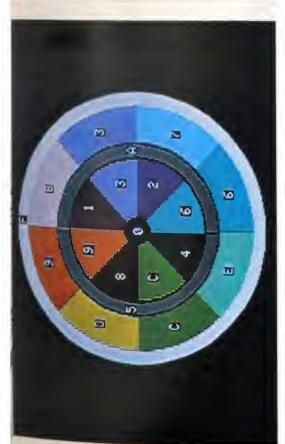

#### The MMU, IOU, and Timing HAL

18' K 40.79

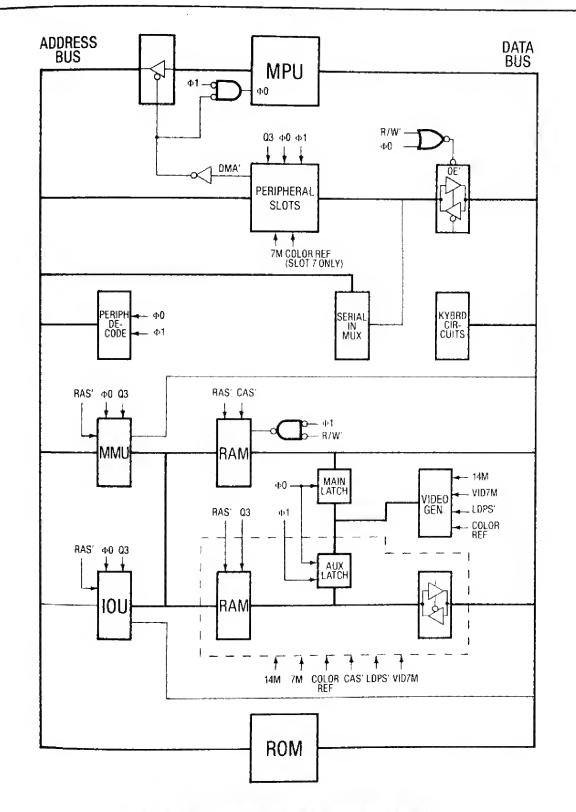

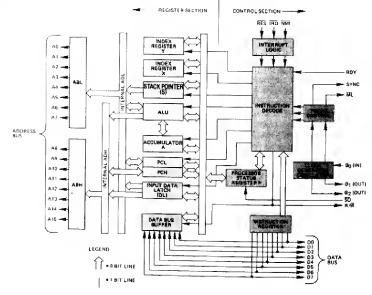

In addition to fundamental building blocks like the MPU, ROM, RAM, and an I/O capability, a microcomputer has a large amount of associated circuitry that supports the operation of the fundamental building blocks. In the Apple IIe, much of this circuitry is concentrated in two custom VLSI (Very Large Scale Integration) ICs, the MMU and the IOU. These custom ICs are very complex integrated circuits, co-designed by Apple and an IC manufacturer\* to perform logical functions required in the Apple IIe.

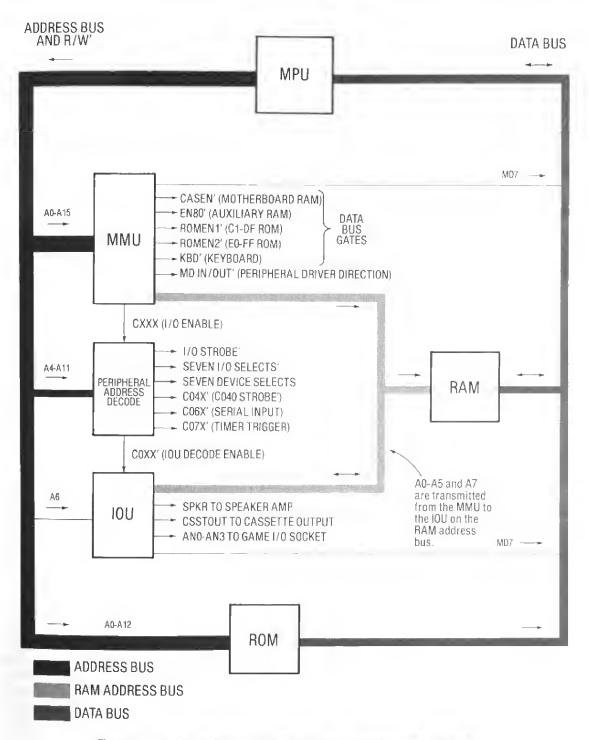

The **MMU** (Memory Management Unit) contains programmable soft switches and address decoding circuitry which define the overall memory and I/O configuration of the Apple IIe. By this, it is meant that the MMU controls which device (RAM, ROM, I/O device, or peripheral card) responds to which addresses. This is a complex task in the Apple IIe, because the memory map can be reconfigured so that the same device does not always respond to a given range of addresses.

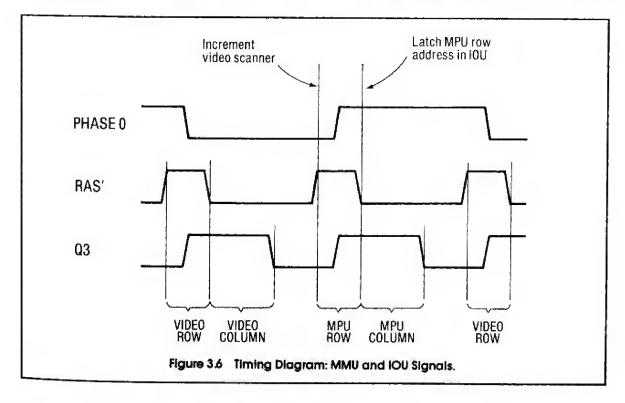

Programmable soft switches are very important in the operational scheme of the Apple IIe. They are like a mechanical switch, except that they are switched when they are addressed by the MPU, not by the flip of a finger. Programs maintain control of a number of Apple IIe functions by setting and resetting soft switches that are mechanized in the MMU and IOU. As an example, the RAMRD soft switch is a programmable switch in the MMU that, when set, enables MPU reading from much of auxiliary card RAM. It is set when the controlling program causes the MPU to perform write access to \$C003 and reset when the program causes the MPU to perform write access to \$C002. The MMU accomplishes its memory management functions by monitoring the address bus and R/W', and responding to certain addresses by setting or resetting its configuration soft switches. Also, for any address on the address bus and any status of the MMU soft switches, the MMU controls which class of motherboard device will respond to an address. The MMU does this by activating or deactivating various data bus management signals. A second function of the MMU is to convert the MPU address from the 16-line address bus format to the 8-line multiplexed format that is required by dynamic RAM. This subject and all subjects related to the MMU are covered in detail in Chapters 2 and 5.

The IOU (I/O Unit) contains circuitry primarily related to the various facets of generating the Apple IIe VIDEO signal. This includes the video scanner, a counter that scans RAM for video output when the MPU is not accessing RAM. It also includes circuitry to convert video scanner states to a multiplexed RAM address, soft switches by which the display mode of the Apple IIe is established, and circuitry which is actively involved in processing the RAM resident display map to generate the VIDEO signal.

In addition to the display related functions mentioned above, several I/O functions of the Apple IIe are implemented in the IOU. These include parts of the cassette and speaker output functions, the annunciator outputs, the KEYSTROBE (keyboard strobe) soft switch, the keyboard auto repeat function, and the capability to transmit the AKD (Any Key Down) line to a line of the data bus so a program can determine when a keyboard key is being held down. The varied IOU tasks span topics covered in several chapters of Understanding the Apple IIe. Figure 1.1 is a general diagram of the IOU that shows chapters and figures in which the IOU functions are discussed and illustrated.

A third special purpose VLSI IC on the Apple IIe motherboard is the **timing HAL**. A HAL (Hard Array Logic) is an IC, designed by a manufacturer to perform logic functions within a general format. The specific logic functions that the IC is to perform are specified by the buyer—in this case, Apple Computer, Inc. The timing HAL is similar to a ROM, except that the HAL purchaser specifies logic functions instead of memory contents.

The HAL in the Apple IIe is used in the process of generating the timing signals that synchronize functions throughout the motherboard. The nature of these timing signals and the details of their generation are discussed in Chapter 3.

<sup>\*</sup>Custom IC design is a cooperative effort by IC and equipment manufacturers. In the case of the IOU and MMU, Apple employee (and former Synertek employee) Walt Broedner designed the IOU and the MMU within the constraints of the Synertek custom IC program. Synertek is the primary MMU and IOU source, and judging by the IOU in my Apple IIe, American Microsystems (AMI) is an alternate source.

# 1-6 Understanding the Apple Ile

Figure 1.1 IOU Functions and Pin Assignments.

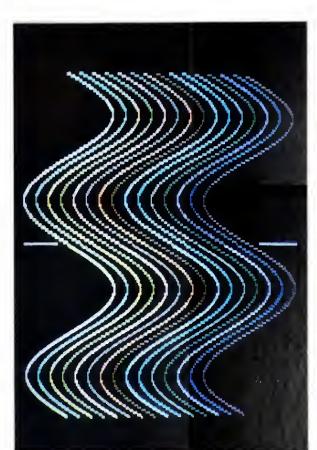

#### Video Output

, de la constante de la const

The primary output of the Apple IIe is video. This video is color compatible with the television system used in the country in which an Apple IIe is sold. There are two versions of the motherboard—one which outputs video compatible with the NTSC television system used in America and other areas, and one which outputs video compatible with the PAL television system used in most of western Europe and other areas. An Apple IIe in a given country will contain the version of the motherboard compatible with that country's television system. Additionally, the video and keyboard ROMs will be tailored to the requirements of that country's language or languages.

Video from the Apple IIe can be directly input to a color or monochrome video monitor but not to a television set. Rather than video, a television accepts RF (Radio Frequency) modulated by video. This means that you can use the Apple IIe with a television set, but the input to the television must be an RF signal modulated by Apple IIe video. Generation of the RF signal and modulation is accomplished in a user supplied modulator. Another name for the user supplied modulator is a pain in the neck.

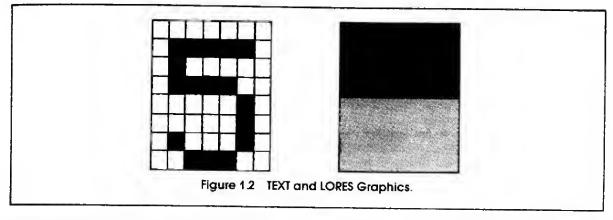

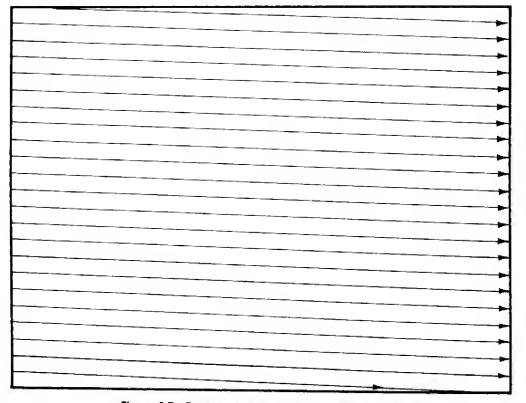

There are three basic Apple IIe video display modes: TEXT, LORES graphics (LOw RESolution colored blocks) and HIRES graphics (HIgh RESolution colored points). Additionally, LORES and HIRES graphics can be displayed with four lines of text at the bottom of the screen in the Apple IIe MIXED mode. MIXED mode is very useful, as far as it goes, because there are many times when the graphics programmer needs to enhance a display with text. However, four lines at the bottom turn out to be inadequate for many purposes. The HIRES screen has good enough resolution to draw text, and several programs are available that make it relatively easy to place upper/lower case text on the HIRES screen. This type of text can be drawn alongside graphics to enhance graphic displays.

All display modes can be switched to normal horizontal resolution (40 TEXT characters, 40 LORES blocks, or 280 HIRES points) or double horizontal resolution (80 TEXT characters, 80 LORES blocks, or 560 HIRES points). The SINGLE-**RES** (single horizontal resolution) modes are identical to the display modes of the older Apple II computer. The **DOUBLE-RES** (double horizontal resolution) modes offer twice the characters, blocks, or points per horizontal display width as do the SINGLE-RES modes. Memory scanning is used to generate video in all Apple IIe display modes. Data that represents the display is stored (mapped) in RAM so that video is generated by processing data that comes from RAM as it is scanned repeatedly. Certain areas of RAM are designated as display memory. The designated areas are:

| TEXT/LORES | Page 1 | \$400-\$7FF  | (1K RAM)  |

|------------|--------|--------------|-----------|

| TEXT/LORES | Page 2 | \$800-\$BFF  | (1K RAM)  |

| HIRES      |        | \$2000-\$3FF |           |

| HIRES      | Page 2 | \$4000-\$5FF | F(8K RAM) |

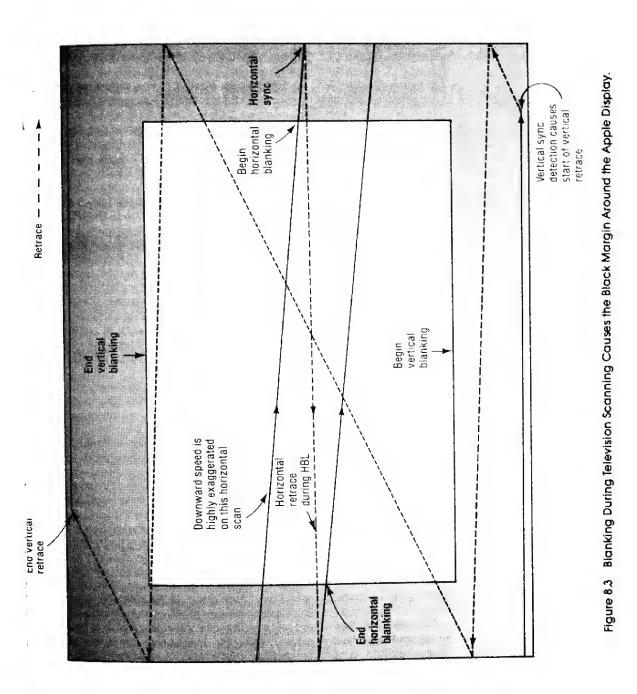

As an example, assume that the computer is in TEXT mode, page 1. Then memory in the range \$400-\$7FF will be scanned approximately 60 times a second and the data in that memory area will be processed for video output. Part of display memory is always being scanned while the computer is on. The Apple IIe is designed so that this constant scanning satisfies the refresh requirement of the dynamic RAM.

Page 1 and page 2 are primary and secondary memory display areas that are switched via the PAGE2 IOU soft switch. Page 1 is normally selected in all modes (PAGE2 soft switch reset), but use of page 2 may suit the programmer's purpose.

An important consequence of the Apple IIe display implementation is that the video display steals memory from the user. The programmer must program around the display areas if he intends to use the associated displays.

SINGLE-RES displays are mapped in motherboard RAM only. One byte of the display map is processed for each cycle of the MPU, and 40 bytes of the display map are scanned to process the displayed portion of a single horizontal scan of the television or monitor. Based on the number of bytes that make up the displayed portion of a horizontal scan, the SINGLE-RES TEXT, LORES, and HIRES modes will be referred to in this book as the TEXT40, LORES40, and HIRES40 modes when it is necessary to distinguish them from their DOUBLE-RES counterparts. For the reason made clear in the next paragraph, the DOUBLE-RES TEXT, LORES, and HIRES modes will be referred to as the TEXT80, LORES80, and HIRES80 modes.

DOUBLE-RES displays are mapped in motherboard RAM and auxiliary card RAM. For every MPU cycle, first one byte of the auxiliary card display map, then one byte of the motherboard portion of the display map are processed to generate video. A total of 80 bytes of the overall display map are scanned to process the displayed portion of a single horizontal scan of the television or monitor. If these are numbered 0—79, the even bytes are stored in auxiliary card RAM, and the odd bytes are stored in motherboard RAM.

A RAM card must be installed in the auxiliary slot to utilize the DOUBLE-RES modes of the Apple IIe. A 64K auxiliary RAM card enables use of all DOUBLE-RES modes, and a 1K auxiliary RAM card enables use of only the TEXT80 mode (80column text).\* Additionally, a 1K auxiliary RAM card enables use of LORES80 mode if a wire is connected between pins 50 and 55 of the 1K RAM card's edge connector.

Scanning for video output is not performed by the MPU but by the IOU. Inside the IOU, there is a counter whose outputs are used to make up the video RAM address, a television sync signal, and other video related signals. This counter synchronizes the television scan to its addressing of RAM and can be thought of as scanning RAM while it scans the television (or video monitor) picture. Consequently, it is referred to in this book as the video scanner.

The scanner accesses RAM in a way that is completely transparent to the MPU. During the first half of every 6502 cycle period, the video scanner accesses motherboard and auxiliary card RAM. During the second half, the 6502 accesses motherboard RAM, auxiliary slot RAM, or other device. The scanner access to RAM is always a read access and the data which comes from RAM during the scanner access is saved and processed by the video generator to make video. The 6502 access can be either read or write and, on some cycles, the 6502 may not access RAM at all.

The programming method for controlling the Apple IIe display is to select the display mode by setting or resetting soft switches, and to compute or look up the memory addresses of screen locations and modify those addresses to achieve the desired display. The video scanner scans the display area determined by the display mode, and the resulting memory data is processed as text or graphics as determined by the display mode.

TEXT characters are represented in the RAM display map as ASCII (American Standard Code for Information Interchange). In addition to ASCII, code for normal display (white on black), inverse display (black on white), or flashing display (alter-

nating normal and inverse) are stored for each text character. One character is stored per byte of display memory. As text is scanned, the coded data from memory is translated to  $5 \times 7$  dot matrix video in normal, flashing, or inverse format. There are 96 displayable upper case, lower case, numeric, punctuation, and special text characters, all of which can be displayed in normal or inverse format and 64 of which can be flashed between normal and inverse format. The TEXT display is 40 columns by 24 lines in SINGLE-RES mode and 80 columns by 24 lines in DOUBLE-RES mode.

The 80-column text capability of the Apple IIe is implemented in hardware and in firmware so that the Apple IIe emulates an Apple II with an 80column card installed in Slot 3. This emulation is carried out to such an extent that the Apple IIe is, in fact, a 40-column display computer with a peripheral 80-column capability. The Apple IIe powers in 40-column mode, and it will remain in that mode up until a program, maybe or maybe not guided by operator input from the keyboard, selects the 80-column mode.

LORES graphics is a programmable display of 40 columns and 48 rows (SINGLE-RES) or 80 columns and 48 rows (DOUBLE-RES) of colored blocks. Each block can be any one of 15 colors including black and white. Apple claims 16 colors but the two grays are identical in color and luminance. There are, however, 16 different LORES patterns, even though they produce only 15 discernible colors, and these will be referred to as the 16 LORES colors.

LORES is mapped in the same display area as TEXT, so memory scanning is identical in the two modes. In LORES, rather than converting ASCII to video, the video generator processes the bit pattern directly into video. The code for each LORES block requires four bits, so there is code for two blocks in every byte of display memory. Also, there is a direct correspondence between the screen location of a pair of LORES blocks and one text character as shown in Figure 1.2.

HIRES40 graphics mode is a programmable array of 280 columns and 192 rows of dots. Because of the way video is generated in the Apple IIe, the color of any dot is dependent on its horizontal position. To draw a violet horizontal line, for instance, every other dot in one row is turned on. To draw a violet figure, only half of the columns of dots can be turned on. This is also true of the other HIRES40 colors: green, orange, and blue. There is only 140 x 192 resolution when drawing these four colors.

<sup>\*</sup>The DOUBLE-RES graphics modes are not available on Revision A motherboards.

White (the absence of color) and black (the absence of luminance) can also be displayed. The 280 dots in any row are divided into 40 groups of seven dots. Each group of seven dots may be shifted together horizontally one half of a dot position, changing the colors of any colored dots in that group of seven. Thus, there are 560 horizontal dot positions in each row, but only 280 dots are independently programmable.

HIRES80 graphics mode is a programmable array of 560 columns and 192 rows of dots. Each dot in the array is independently programmable, and the horizontal resolution is so fine that all 16 LORES colors can be produced, and no shifting of 7-dot patterns is required or available. Resolution is 560 x 192 in monochrome plotting, and varies from 140 x 192 to 560 x 192 in 16-color plotting depending on color.

This brief statement of HIRES graphics capabilities is probably just enough information to let the reader know that the subject of HIRES is complex. Full understanding is possible in the light of more detailed analysis, and HIRES is covered in greater detail in Chapter 8. For now, let the resolution of the Apple IIe HIRES display be summarized as varying from 140 x 192 to 560 x 192 depending on color or monochrome plotting and selection of HIRES40 or HIRES80 mode.

The HIRES memory display area is much larger than the TEXT/LORES area: 8192 bytes of motherboard RAM for a HIRES40 display, and 8192 bytes of motherboard RAM and 8192 bytes of auxiliary card RAM for a HIRES80 display. This is the hardware cost of high resolution.

#### The Keyboard

The keyboard is the primary human input to the Apple IIe (as opposed to storage media input such as

cassette or disk). Virtually all human alphanumeric input is via the keyboard, and the MPU of the Apple IIe spends the majority of its life cycling through a little firmware routine called KEYIN (or GETKEY if the 80-column firmware is active). This routine samples the keyboard to see if a key has been pressed, while incrementing a random number counter and occasionally flashing the screen cursor. KEYIN checks the keyboard at a rate of about a 165 million times an hour, and if anyone asks you what an Apple does, you can answer "mainly, it checks to see if a key has been pressed."

Enough silliness. The keyboard has 63 keys that represent letters of the alphabet, numbers 0-9, punctuation characters, symbolic characters, and special functions. These keys are arranged like those of the keyboard of an IBM *Sclectric* typewriter. An auto repeat function (mechanized in the IOU) simulates rapid keypresses when a key is held down constantly, and provisions exist for programs to determine when a key is being pressed or when a key has been pressed. Apple He keys "roll over", meaning that if one key is held and another is pressed, the newly pressed key will be read by the controlling program.

Most of the keys produce ASCII which can be read by a program, and most of the ASCII keys, including the alphabetic keys, produce shifted ASCII if the left or right SHIFT key is held down simultaneously with the ASCII producing key. Since the keyboard input and text output are both ASCII, it is fairly easy to output characters to the video display as they are entered from the keyboard. This is done by keyboard input and video output routines in the Apple IIe firmware.

Special function keys on the keyboard are ESC, DELETE, RESET, TAB, CONTROL, RETURN, SHIFT, CAPS LOCK, open Apple, close Apple, left arrow, right arrow, down arrow, and up arrow. CONTROL and SHIFT modify the ASCII produced by other simultaneously pressed keys while CAPS LOCK is a 2-position locking switch that forces upper case ASCII from the alphabetic keys when it is latched in the down position. RESET is tied to Apple IIe RESET' line, and if CONTROL and RESET are pressed simultaneously, RESET' drops low to reset the Apple IIe. Resetting the Apple IIe consists of resetting the 6502, all MMU soft switches, most IOU soft switches, and all peripheral cards that respond to RESET'.

ESC, DELETE, TAB, RETURN, left arrow, right arrow, down arrow, and up arrow produce ASCII which must be interpreted by the controlling program. The codes for ESC and DELETE are unique, but TAB, RETURN, left arrow, right arrow, down arrow, and up arrow produce code that is identical to that of CONTROL-I, CONTROL-M, CONTROL-H, CONTROL-U, CONTROL-J, and CONTROL-K respectively.

The open Apple and close Apple keys are not associated with other keyboard functions. Instead, these are connected to the PB0 and PB1 serial inputs described in the next section. Pushing open Apple or close Apple is equivalent to pushing pushbutton 0 or pushbutton 1 on a paddle set or joystick, and these keys are mounted on the keyboard only to provide a convenient means of activating the PB0 and PB1 input lines.

All ASCII produced by Apple IIe keypresses comes from the **keyboard ROM** which is a standard 2K ROM. This ROM contains ASCII for a standard keyboard layout and an alternate keyboard layout. The alternate layout is a Dvorak layout\* in American Apple IIe's. In export versions, it is usually a layout tailored to the requirements of the host country's primary language. The alternate layout can be selected by installing a switch assembly as shown in an application note at the end of Chapter 7.

While there is no numeric keypad built into the Apple IIe keyboard, there is a jack on the motherboard which accepts a numeric keypad. Like ASCII from the main keyboard, ASCII from this external keypad comes from the keyboard ROM, so the keys of a keypad can be defined as desired by installing a customized keyboard EPROM on the motherboard.

#### Other I/O

I/O is Input/Output. Our point of reference for this discussion is the motherboard, meaning that we

speak of input to the motherboard and output from the motherboard. The peripheral slots give the Apple IIe an extremely versatile I/O capability, but there is a good deal of additional I/O circuitry built into the Apple IIe. The keyboard input and video output are the most significant motherboard I/O. There are also some useful serial I/O ports.

Serial data is data on one line. This is opposed to parallel data on more than one line (eight lines, for instance). To transfer eight bits serially, each bit of information is placed on the same line one after another. This takes eight times as long as an 8-bit parallel transfer, but requires only one connecting wire. The keyboard is a parallel input. The video is not a simple digital output but a mildly complex signal output with a serial data component. In addition to these I/O capabilities, there are eleven serial I/O ports and four resistance sensitive timer inputs.

The speaker output is a serial output port connected to a speaker through an audio amplifier. The cassette input and output are serial data transmitted via audio phone jacks on the motherboard accessible from the back of the case. They are designed to connect directly to the earphone output and microphone input of a common audio tape recorder. Firmware routines in motherboard ROM read and write cassette data in Apple's storage format.

Usage of 5 ½ inch floppy disks is so prevalent that cassette storage is rarely used by most Apple owners. Floppy disk I/O is not a built-in capability of the motherboard, so the disk electronics are contained in the drive and on a peripheral card called the disk controller. Disk data is transferred in parallel between the MPU and the controller, and serially between the controller and the drive. Control of disk I/O requires an extensive program, and the most commonly used program of this nature is **DOS 3.3** (Disk Operating System, version 3.3), a product of Apple Computer, Inc. A more recently developed DOS, and the one which is the current focus of support by Apple, is called **ProDOS**.

The other serial I/O signals are TTL (Transistor Transistor Logic) compatible. TTL is a very common logic family of integrated circuits used for digital logic. The logic devices on the Apple IIe motherboard are either TTL or interface directly to TTL.\* TTL devices operate with two voltages corresponding to the two states of digital logic. The

<sup>\*</sup>Dvorak is keyboard layout designed to permit faster typing than is possible in the conventional QWERTY layout.

<sup>\*</sup>Most TTL chips in the Apple IIe are LSTTL (Low Powered, Schottky-Barrier diode clamped TTL). The 6502, ROM, RAM, the MMU, the IOU, and the keyboard decoder are TTL compatible MOS (Metal Oxide Semiconductor) chips.

TTL low voltage is 0 to 0.8 volts, and the TTL high voltage is 2.4 to 5 volts. These are the two voltage levels which represent digital information throughout the Apple IIe.

There is a 16-pin DIP (Dual In line Package) socket on the Apple IIe motherboard which is generally called the **game I/O connector**. A set of two paddles, a joystick, or a resistive graphics pad is normally connected here, but there is a capability for multiple uses. Four of the pins are **annunciator** outputs. These are output lines which can be independently switched to a TTL high or low level by the controlling program. A fifth TTL output is called a **strobe**. This output is high unless a program triggers it. It then goes low for just 0.5 microseconds (half of a 6502 cycle), then returns to its normal high state.

There are three TTL input ports on the game I/O connector which can be read by a program. Two of these, PB0 and PB1, are normally connected to **pushbuttons** on the joystick, paddles, or graphics pad. PB0 and PB1 are also connected to the keyboard open and close Apple keys respectively. Additionally, if the motherboard X6 jumper is soldered, the SHIFT' line is connected to PB2 so that the left and right SHIFT keys activate this third game I/O TTL input.

The paddles themselves are just potentiometers (variable resistors). Joysticks are two potentiometers mechanically linked so that the resistance of one potentiometer represents horizontal motion and the resistance of the other potentiometer represents vertical motion. Game I/O graphics pads consist of X-ordinate and Y-ordinate resistive surfaces arranged and wired so that the X and Y resistances vary with the point on the pad at which pressure is applied.

In addition to the game I/O socket, the four timer (paddle) and three TTL (pushbutton) inputs are connected to a game I/O extension jack in the back of the Apple IIe. This 9-pin jack provides a means of connecting a paddle set, joystick, or other device to the Apple IIe without lifting the cover. Furthermore, when a device is connected to this extension jack, the game I/O lines which are not used by the extension jack device are available at the game I/O socket for connection to other devices.

### The Power Supply

Household power measures from 100 to 220 Volts AC (Alternating Current), depending on the country in which the house is located. Most of the circuits in the Apple IIe, however, require +5 volts DC (Direct Current) referenced to ground (0 volts). Converting relatively high voltage, household AC power to the required low voltage DC power required by the Apple IIe is the function of the **power supply**.

The power supply in an Apple IIe is designed to operate on the household power in the country in which it is sold. In any country, the Apple IIe power supply generates +5, -5, +12, and -12 volts DC referenced to ground. These voltages are distributed throughout the motherboard to any device that needs them. Additionally, all four voltages and ground are available at the peripheral slots to supply power to peripheral cards, and +5 VDC and ground are available at the auxiliary slot to supply power to an auxiliary card.

#### SUMMARY

The Apple IIe is a single board, 6502 based microcomputer with built-in memory and video generation circuitry. It is an improved version of the older Apple II computer. Enhancements include full upper and lower case text handling capability, 80column text video display, and 128K of motherboard and auxiliary slot RAM, as opposed to the upper case only, 40-column, 48K Apple II.

The Apple IIe circuit board contains seven peripheral slots and an auxiliary slot which hold smaller boards, and it is therefore thought of as a motherboard. The slots give the Apple IIe expansion and I/O capabilities comparable to more expensive card cage microcomputer designs.

The motherboard can be one of two versions—one which outputs video that is color compatible with the NTSC television system used in America, or one which outputs video that is color compatible with the PAL television system used throughout western Europe except in France. An Apple He in a given country will contain the version of the motherboard compatible with that country's television system. Additionally, the video and keyboard RAM will be tailored to the requirements of that country's language or languages.

The 6502 in the Apple He operates at 1.0205 MHz. IRQ', NMI', RESET', and READY signals to the 6502 are connected to the peripheral slots. The DMA' signal enables peripheral cards to isolate the MPU from the rest of the motherboard. This enables control of the Apple He from secondary MPUs or other DMA devices in the peripheral slots. MPU control of the various hardware features is via address decoding. The motherboard contains 65,536 bytes of dynamic RAM, and motherboard circuitry fully supports an additional 65,536 bytes of dynamic RAM in an auxiliary slot RAM card. 16,128 bytes of firmware include Applesoft BASIC and a system monitor containing a number of important utilities.

In addition to the MPU, RAM, and ROM, there are three important special purpose ICs that implement Apple IIe motherboard logic functions. The MMU controls the overall configuration of the Apple IIe memory map; the IOU performs multiple functions related to generation of the video display and other I/O; and the timing HAL contains most of the circuitry required for the generation of Apple IIe timing signals. The controlling MPU program manipulates overall memory configuration, the video display mode, and some I/O functions by setting or resetting programmable MMU and IOU soft switches.

The video output is compatible with a video monochrome or color monitor. It can be used with a home TV when connected through an inexpensive modulator. Either single or double horizontal resolution displays can be produced by programs, although an auxiliary slot RAM card is necessary for use of the DOUBLE-RES display modes. All DOUBLE-RES displays are available with a 64K auxiliary RAM card, but a 1K RAM card only supports DOUBLE-RES text or, with a minor RAM card modification. DOUBLE-RES LORES graphics.

TEXT is upper and lower case, 5 x 7 dot matrix representation in a 40 character by 24 line (SINGLE-RES), or 80 character by 24 line (DOUBLE-RES) display. There are 96 video text characters, all of which can be displayed normally (white on black) or inverted (black on white). Sixty-four of the text characters can be flashed between normal and inverse display. This includes numerals, punctuation, and upper case alphabetic characters but excludes lower case alphabetic characters.

Graphics modes include 40 x 48 (SINGLE-RES) and 80 x 48 (DOUBLE-RES) LORES block modes in 15 colors, 140 x 192 HIRES point mode in six colors (SINGLE-RES), 280 x 192 HIRES point mode in black and white (SINGLE-RES), 140 x 192 HIRES point mode in 15 colors (DOUBLE-RES), 140 x 192 to 560 x 192 HIRES point mode in 15 colors with color dependent resolution (DOUBLE-RES), and 560 x 192 HIRES point mode in black and white (DOUBLE-RES). Some capabilities exist for mixing text and graphics.

The video display in all modes is mapped in certain areas of RAM, motherboard RAM in the SINGLE-RES modes, and both motherboard and auxiliary card RAM in the DOUBLE-RES modes. IOU circuitry continuously scans one of four possible areas in motherboard and auxiliary card RAM while RAM output is processed to generate video. RAM addressing is time shared between the system address bus and the IOU video scanner. 6502 access to RAM alternates with video scanner access so, while the 6502 operates at 1 MHz, motherboard and auxiliary card RAM are accessed at 2 MHz. In the process of scanning RAM for video output, the RAM is refreshed.

In addition to video output and the I/O capabilities inherent with the peripheral slots, there are a cassette input port, a cassette output port, a speaker, four TTL control outputs, one .5 microsecond TTL output strobe, four resistance sensitive timer inputs, three TTL inputs, a keyboard, and a numeric keypad jack. Two of the TTL inputs can be activated by pressing the open or close Apple switches on the keyboard.

The keyboard contains 63 key switches arranged like those on an IBM *Selectric* typewriter, and is adequate for most text processing functions. Operational features include a CAPS LOCK key, n-key rollover, and automatic simulation of rapid keypresses when a key is held down (auto repeat). An alternate keyboard layout is electrically selectable, but a switch assembly must be installed to access the alternate layout. Also, because of the versatile nature of the motherboard keyboard circuitry, the keyboard layout can be changed by simply replacing a ROM on the motherboard.

The built-in Apple IIe power supply provides +12, -12, +5, and -5 volts DC referenced to ground. These voltages and ground (0 volts) are distributed throughout the motherboard and to the seven peripheral card slots. +5 volts and ground are also connected to the auxiliary slot.

# chapter 2

# The Bus Structure of the Apple IIe

There are many signals distributed throughout the Apple IIe, but the most fundamental data transfer takes place on the data bus, and the most basic control information is distributed via the address bus. To understand how the Apple IIe and other microcomputers really work, it is very important to understand the bus structure. Fortunately, it's not that hard to understand. The basic concepts of the bus structure are within the grasp of nearly everyone who uses a microcomputer.

The bus structure is a natural starting point for learning what really goes on inside the Apple computer. Discussing the bus structure will lead naturally to the discussion of the other microcomputer elements that the bus is connected to. First, though, we need to find out what a bus is and how it is used.

#### COMPUTER BUSES AND THREE STATE LOGIC

Logic signals in the Apple are distributed electrically via conductive paths on the motherboard. When a number of signals are grouped functionally and distributed throughout a microcomputer, they are collectively referred to as a bus. Physically, then, a bus is an electrical distribution of multiline information. In the Apple, the **address bus** is a **sixteen**-line electrically distributed information group, and the **data bus** is an **eight**-line electrically distributed information group.

Some devices connected to a bus are strictly receivers of information. ROM is like this in its connection to the address bus. Receivers respond to the high/low information on the lines of the bus without appreciably affecting the bus information. Electrically speaking, the receiver input presents a high impedance to the bus which enables other devices to bring the bus lines high or low. If impedance is a new word to you, it may help to think of high impedance as high isolation.

Some devices on a bus must be information transmitters capable of bringing the bus lines high or low. If more than one information transmitter is connected to a bus, each transmitter must be able to disconnect itself from control of the bus by presenting a high impedance to the bus. Only one device can control the bus at a time. Instead of two state, the outputs of these devices are said to be three state or tri-state. The three states are high voltage, low voltage, and high impedance. All information transmitters to the data bus of the Apple are capable of presenting these states to their bus connections. The ROM output to the data bus is a typical three state output.

A third type of device, capable of transmitting to or receiving from a bus, is called a **transceiver** (transmitter/receiver). The MPU, for instance, receives (reads) data from and transmits (writes) data to the data bus, so as far as the data bus is concerned, the MPU is a transceiver. While the MPU is reading, it presents a high impedance to the data bus so the addressed device can place data on the data bus. While the MPU is writing, it controls the data bus.

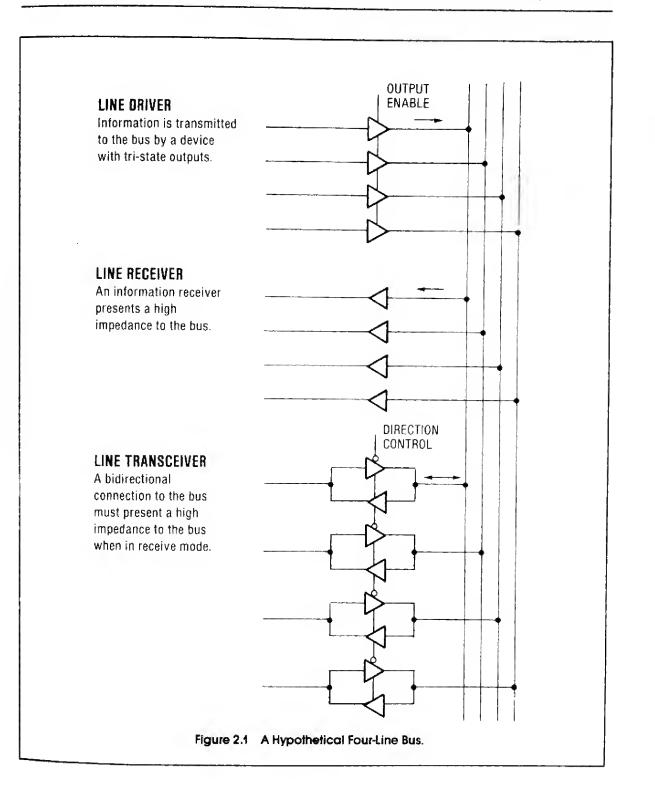

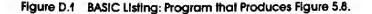

Figure 2.1 shows a hypothetical 4-line bus. The symbols shown are schematic representations of a tri-state line driver, a line receiver, and a line transceiver. A triangle represents a single line driver. Triangles with a control line coming in from the side are tri-state line drivers. A little circle at a control input to a triangle means that the input is active when its voltage is low. Here is a truth table for the tri-state line driver shown in Figure 2.1:

| OUTPUT<br>ENABLE | OUTPUT         |

|------------------|----------------|

| Low              | High Impedance |

|                  | High<br>Low    |

|                  | ENABLE         |

The control line either enables the high/low output or forces the output to high impedance. The high/ low output, when enabled, follows the input.

It can be seen that the **output enable** controls of the various information transmitters are the key to cohesive control of the bus. For a bus with many possible information transmitters, like the data bus of the Apple, there has to be some intelligent management of the various tri-state output enables. We will see shortly how this is accomplished. In the following discussions, remember that when a device like a ROM chip responds to an address prompt by placing data on the data bus, this is accomplished via an output enable to the tri-state outputs of the ROM chip.

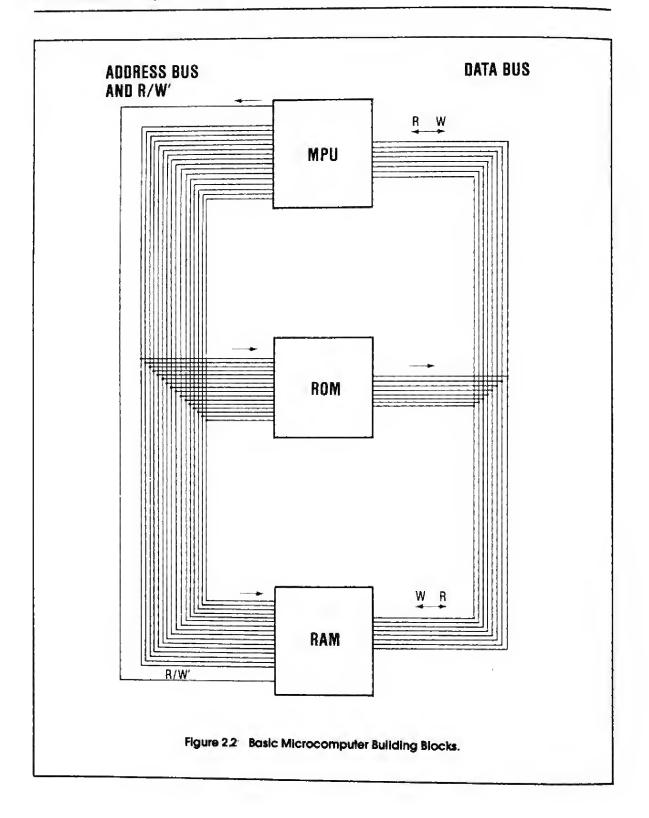

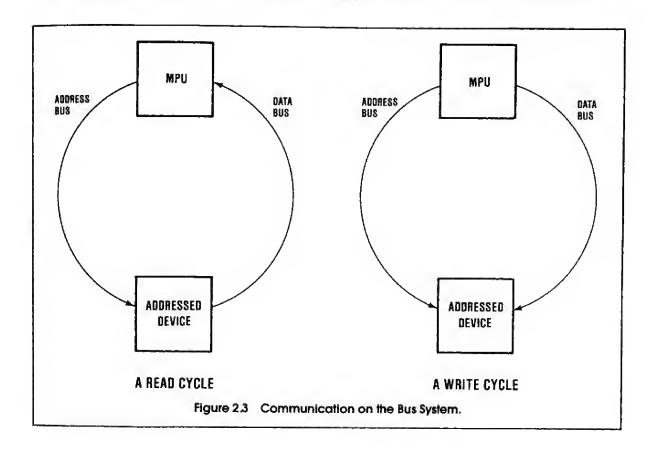

Figure 2.2 shows a highly simplified diagram of the bus structure of the Apple IIe. There are two distinct multiline signal paths: the address bus and the data bus. The R/W' line (Read/Write control) is shown separate and can be thought of as an extension of the address bus controlling the direction of data flow on the data bus. Communication takes place on every 6502 cycle between the MPU and an addressed device. Data flows between the MPU and the device in a direction determined by the R/W' line. The MPU controls the R/W' line and the address bus.

Figure 2.3 shows the two types of bus access which occur in the Apple IIe. In a read access, the MPU places an address on the address bus and reads the data bus. In a write access, the MPU places an address on the address bus and places data on the data bus. This establishes a system of data bus control that had to be implemented in the design of the Apple. The control system works like this:

- 1. When the R/W' line is low (write access), all inputs to the data bus are disabled except the MPU.

- 2. When the R/W' line is high (read access), all inputs to the data bus are disabled except the device which is addressed.

This system concept keeps traffic flow orderly and is a basic feature of microcomputer design.

The only remaining points to be made about buses involve semantics. The peripheral slots are sometimes referred to as the peripheral bus or the Apple bus. In fact, the wiring of the slots fits our description of a bus as a functional group of distributed signals. The slots are a bus whose distributed signals include the address bus, the data bus, and other signals. Up to this point, the discussions have avoided calling the slots a bus only to avoid confusion between the card cage bus and the more basic address bus and data bus. The connections to the RAM and ROM chips form two more distributed signal groups that can be referred to accurately as the RAM bus and the ROM bus. This book will continue to use the word "bus" to refer to the address bus, the data bus, and the extensions of these two basic communications paths. The peripheral bus, RAM bus, ROM bus, and other distributed signals will be referred to using other terminology.

The lines of the various buses in the Apple are referred to by one or more letters followed by a number. For example, the lines of the Apple address bus are referred to as A0 through A15. The largest number, A15 in this example, refers to the line which carries the most significant bit of information. A list of bus terminology used in this book follows here.

ė